【導讀】在FPGA內實現(xiàn)按鍵消抖的方法多種多樣,但是最簡單的是采用移位寄存器的方法進行消抖。因為移位寄存器的方法不需要對時鐘進行分頻,也不需要進行延時等復雜操作。本文就為大家講解這種在FPGA內實現(xiàn)按鍵消抖的方法。

抖動的產(chǎn)生

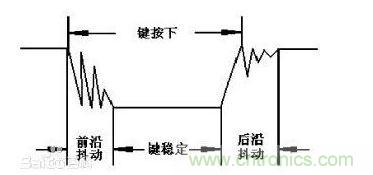

通常的按鍵所用開關為機械彈性開關,當機械觸點斷開、閉合時,由于機械觸點的彈性作用,一個按鍵開關在閉合時不會馬上穩(wěn)定地接通,在斷開時也不會一下子斷開。因而在閉合及斷開的瞬間均伴隨有一連串的抖動,為了不產(chǎn)生這種現(xiàn)象而作的措施就是按鍵消抖。

抖動時間

抖動時間的長短由按鍵的機械特性決定,一般為5ms~10ms。這是一個很重要的時間參數(shù),在很多場合都要用到按鍵穩(wěn)定閉合時間的長短則是由操作人員的按鍵動作決定的,一般為零點幾秒至數(shù)秒。鍵抖動會引起一次按鍵被誤讀多次。為確保FPGA對鍵的一次閉合僅作一次處理,必須去除鍵抖動。在鍵閉合穩(wěn)定時讀取鍵的狀態(tài),并且必須判別到鍵釋放穩(wěn)定后再作處理。

圖1 按鍵抖動

FPGA內實現(xiàn)消抖的方法

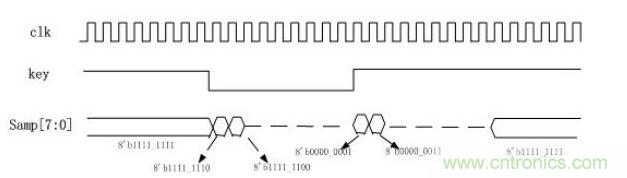

在FPGA內實現(xiàn)按鍵消抖的方法多種多樣,但是最簡單的是采用移位寄存器的方法進行消抖。因為移位寄存器的方法不需要對時鐘進行分頻,也不需要進行延時等復雜操作,即可實現(xiàn)對按鍵邊沿的檢測。假設未按下時鍵值=1.

1、在無鍵按下時,移位寄存器samp[7:0]始終采集到高電平,即samp[7:0]=8''b1111_1111;

2、當鍵按下時,samp[7:0]將采集到低電平,數(shù)據(jù)的變化方式為samp[7:0]=8''b1111_1110-->8''b1111_1100-->8''b1111_1000--> ........——>8''b0000_0000;samp[7:0]=8''b1111_1110即為按鍵下降沿。

3、當松開按鍵時,samp[7:0]將重新采集到高電平,數(shù)據(jù)變化方式為samp[7:0]=8''b0000_0001-->8''b0000_0011--> ........-->8''b1111_1111;當samp[7:0]=8''b0111_1111時,即為按鍵上升沿。

圖2 移位寄存器消抖原理圖

[page]

參考Verilog代碼

//模塊名:EdgeDetect,邊沿檢測

//button:按鍵,無鍵按下時為高電平//clk:10M時鐘

//rst:復位按鈕,低電平有效

//rise:檢測到上升沿,高電平有效,寬度為1個clk

//fall:檢測到下降沿,高電平有效,寬度為1個clk

module EdgeDetect(

input clk,

input rst,

input button,

output reg rise,

output reg fall

);

reg[7:0] samp;//移位寄存器采集button鍵值

//移位寄存器采集button信息

always@(posedge clk or negedge rst)

begin

if(!rst)

samp<=8''b1111_1111;

else

samp<={samp[7:1],button};

end

//產(chǎn)生上升沿信息

always@(posedge clk or negedge rst)

begin

if(!rst)

rise<=1''b0;

else if(samp==8''b1111_1110)

rise<=1''b1;

else

rise<=1''b0;

end

//產(chǎn)生下降沿信息

always@(posedge clk or negedge rst)

begin

if(!rst)

fall<=1''b0;

else if(samp==8''b0111_1111)

fall<=1''b1;

else

fall<=1''b0;

end

endmodule