【導(dǎo)讀】運(yùn)算放大器是指一類專門通過改變外圍器件可以實(shí)現(xiàn)不同算數(shù)運(yùn)算的放大器�。任何一顆運(yùn)放都集成了非常多的晶體管��,這些晶體管除了構(gòu)成基本的工作電路���,同時也會有實(shí)現(xiàn)輸入輸出電壓鉗位等保護(hù)功能����。但是因?yàn)樯a(chǎn)工藝的原因���,在制造這些保證運(yùn)放正常工作的晶體管的過程中�,不可避免地會引入寄生晶體管和二極管��。當(dāng)運(yùn)算放大器工作在規(guī)格書指定的工作范圍內(nèi)時����,這些寄生晶體管不會對芯片的工作造成影響。然而��,如果運(yùn)放工作在超規(guī)格書的范圍時�,可能使得芯片的輸出異常��,進(jìn)入輸出鉗位狀態(tài)���,從而影響電路的正常工作。本文以LM358為例�����,介紹其進(jìn)入輸出鉗位狀態(tài)的機(jī)理����,同時提出避免芯片被鉗位的解決辦法�����。

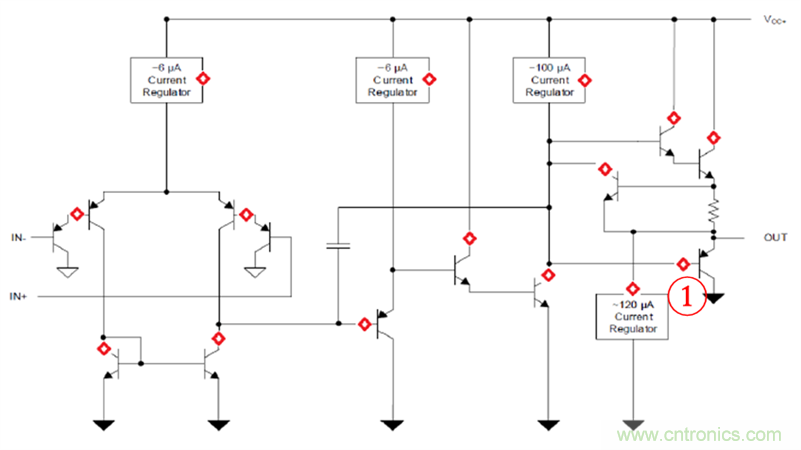

一����、運(yùn)算放大器進(jìn)入鉗位狀態(tài)的原理(以LM358為例)

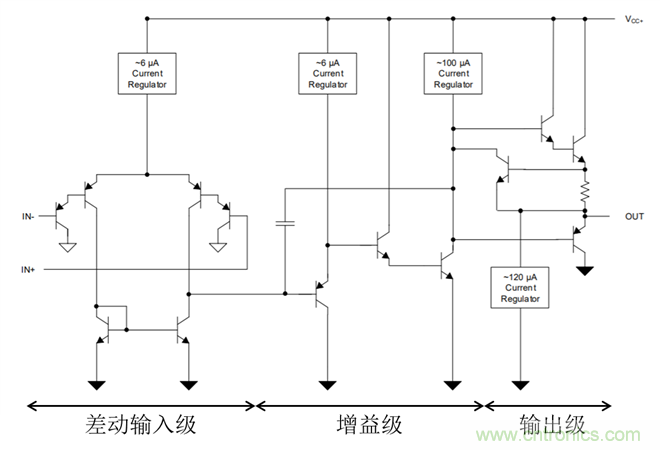

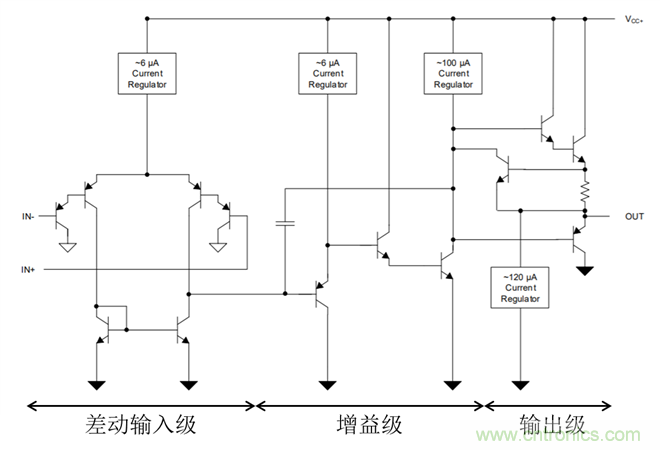

雖然各家廠商推出的運(yùn)算放大器性能與規(guī)格互有差異,但是一般而言標(biāo)準(zhǔn)的運(yùn)算放大器都包含下列三個部分�����。

1.差動輸入級:以一差分放大器作為輸入級�����,提供高輸入阻抗以及低噪聲放大的功能。

2.增益級:運(yùn)算放大器電壓增益的主要來源���,將輸入信號放大轉(zhuǎn)為單端輸出后送往下一級��。

3.輸出級:輸出級的需求包括低輸出阻抗�、高驅(qū)動力��、限流以及短路保護(hù)等功能�。

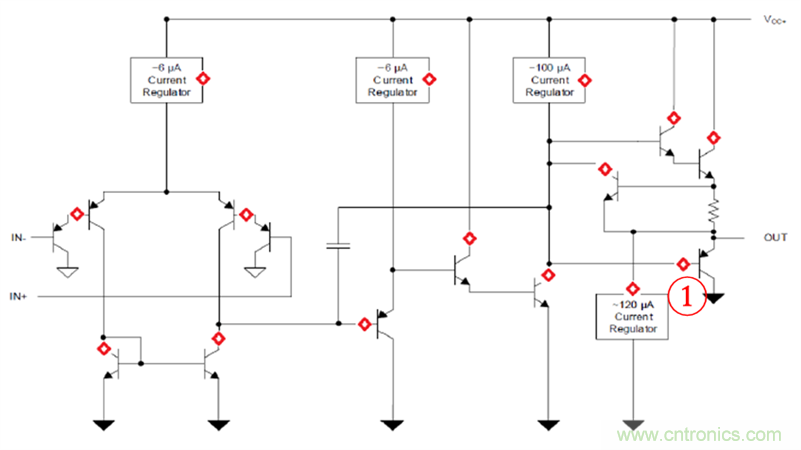

圖1. LM358內(nèi)部架構(gòu)圖

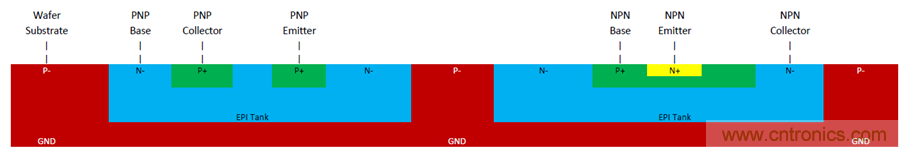

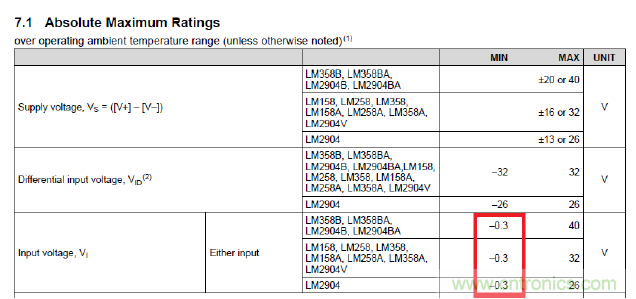

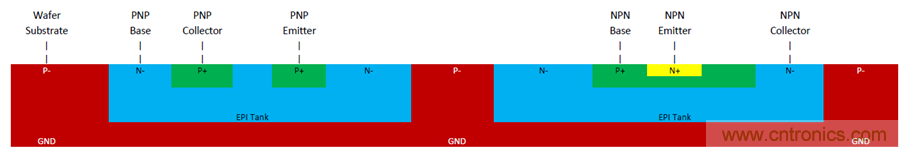

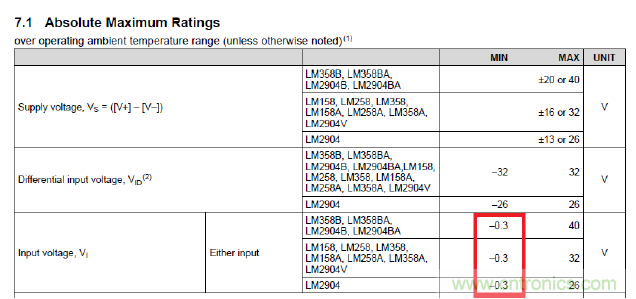

可以看到,所有電路的基本組成單元都是NPN管和PNP管���,這些NPN和PNP管由連接到地的P基底隔開�,如圖2所示�,這個基底將所有三極管隔離開。但是�����,如果LM358的輸入端(PNP的base極)太低�����,低過P基底一個電壓,那么這個偏置電壓就會導(dǎo)致電流流經(jīng)基底��,而使得芯片無法正常工作��。所以LM358的規(guī)格書會規(guī)定其輸入電壓的范圍��,比如最低不能超過-0.3V��。

圖2. 運(yùn)放NPN和PNP管結(jié)構(gòu)示意圖

圖3. LM358的最大電壓范圍

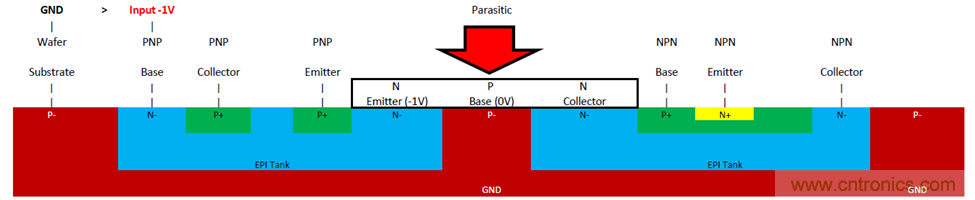

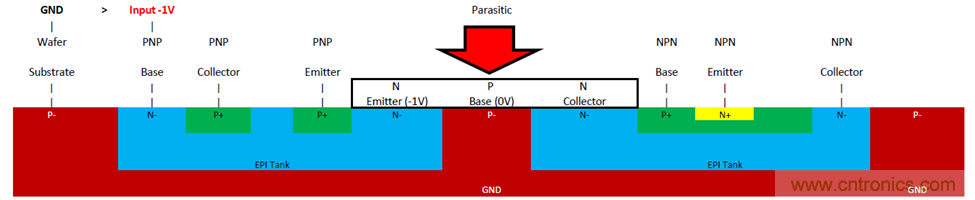

如圖4所標(biāo)注���,PNP管的發(fā)射極�,P基底和NPN管的集電極構(gòu)成了一個寄生的NPN管�����,當(dāng)運(yùn)放的輸入低于-0.3V時(比如-1V)�����,寄生的NPN管的發(fā)射極比基極低-1V���,這個電壓足夠使得寄生的NPN管導(dǎo)通,從而引起電流從集電極流向基極�,這樣���,原本原本隔離開的兩個晶體管之間就有了電氣連接,同時與GND之間也有了電氣連接�,芯片將無法正常工作。

圖4. 運(yùn)放NPN和PNP管和基底構(gòu)成寄生NPN管

圖5用紅點(diǎn)標(biāo)出了LM358所有可能有漏電流的點(diǎn)����,以①點(diǎn)為例,當(dāng)其對地有漏電流時�����,芯片輸出端的PNP管將導(dǎo)通�����,從而使得芯片輸出被鉗位到低電平��。

圖5. LM358可能有漏電流的點(diǎn)

不同地點(diǎn)的漏電流會導(dǎo)致不同的運(yùn)放輸出狀態(tài)����,有些可能使得芯片輸出為高,有些可能使得芯片輸出為低��。對于同樣的輸入,比如IN-輸入為-1V���,其引起的可能有漏電流的地方也隨著芯片layout的不同而不同��,一般離得越近的晶體管之間更容易引起漏電流��,對于同一系列的芯片���,比如LM358和LM358B,由于其裸片的layout不同��,對于同樣的輸入超規(guī)格書使用��,輸出的鉗位狀態(tài)也不同�。

二、鉗位狀態(tài)可能引起的問題及其避免方法

在實(shí)際應(yīng)用過程中�����,絕大多數(shù)工程師都會避免輸入信號的電壓超過規(guī)格書規(guī)定的范圍��,但是���,由于上電順序的影響,運(yùn)放很容易出現(xiàn)被測量信號比電源信號早上電的情況,從而導(dǎo)致芯片超規(guī)格使用從而進(jìn)入鉗位狀態(tài)�。

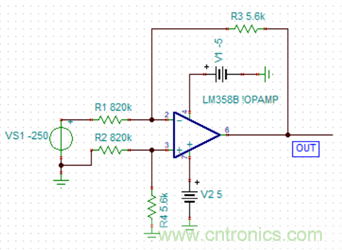

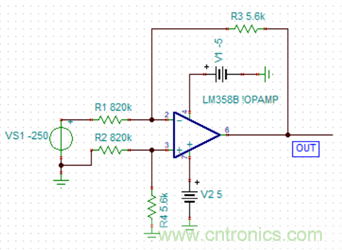

圖6是一個常見的電壓測量電路,LM358B由±5V供電����,很容易可以推算出正常工作時Vout=VS1*(-R3/R1)=-250V*(-5.6/820)=1.71V。

圖6. 電壓檢測電路

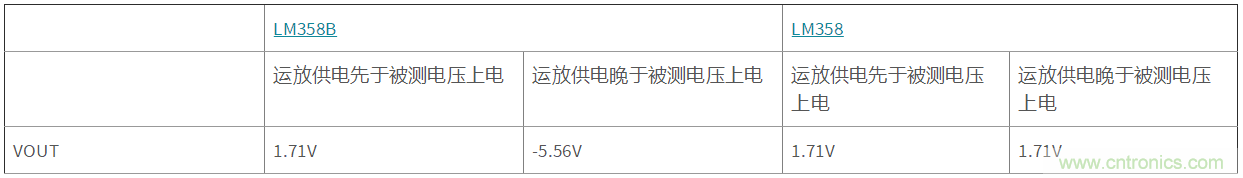

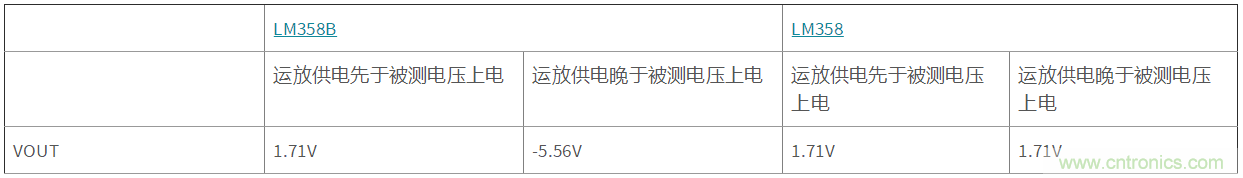

我們在實(shí)際電路中測量��,發(fā)現(xiàn)實(shí)際運(yùn)放的輸出和芯片的上電順序有關(guān)�,如表1所示:

表1. LM358和LM358B輸出實(shí)測值

可以看到,當(dāng)運(yùn)放供電先于被測電壓上電時運(yùn)放的輸出都是正常的���,這是因?yàn)樵谡麄€過程中芯片的輸入電壓都沒有超過電源電壓�,從而符合規(guī)格書的應(yīng)用范圍��。當(dāng)運(yùn)放供電晚于被測-250V電壓上電����,當(dāng)被測電壓上電而運(yùn)放未上電時,運(yùn)放的負(fù)輸入端會有一個低于-0.3V的負(fù)電壓��,根據(jù)第一章的分析��,可能會導(dǎo)致運(yùn)放的輸出鉗位到正電源電壓或者負(fù)電源電壓�����。對于LM358而言,其輸出被鉗位到正電源電壓��,當(dāng)供電電源上電后���,+5V電源會通過輸出端將LM358的輸入端拉回正電壓�����,從而使得芯片的輸出恢復(fù)正常����。而對于LM358B而言��,其輸出被鉗位到負(fù)電源電壓����,當(dāng)供電電源上電后,-5V電源通過輸出端將LM358B的輸入端拉到更低的電壓(實(shí)測為-5.68V)�,這個電壓比負(fù)電源低0.68V,輸出始終被鉗位到負(fù)電源電壓附近無法恢復(fù)正常��。

從上文分析可以看出��,不同的鉗位狀態(tài)可能導(dǎo)致不同的輸出���,由于鉗位狀態(tài)和芯片的layout有關(guān)���,我們無法預(yù)知一顆芯片的鉗位狀態(tài),為了避免異常情況���,針對輸入電壓可能先于電源電壓上電的情況����,我們可以:

1.人為控制上電順序��,保證在整個過程中不會出現(xiàn)輸入電壓超規(guī)格的情況���。

2.在運(yùn)放的輸入端加對地鉗位二極管��,保證在任何上電順序下運(yùn)放的輸入電壓都不會超規(guī)格�����。

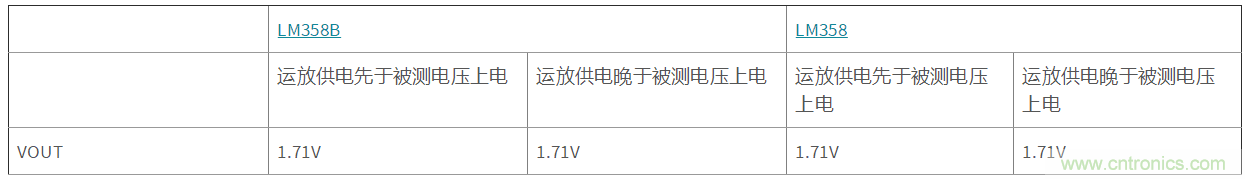

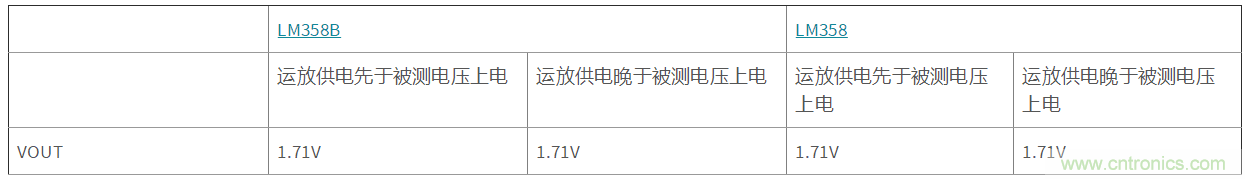

為了驗(yàn)證方法2���,我們在LM358和LM358B的輸入對負(fù)電源加入反向鉗位二極管后實(shí)測的結(jié)果如下:

表2. 加入鉗位二極管后LM358和LM358B輸出實(shí)測值

三���、結(jié)論

1.運(yùn)放的輸入電壓超過規(guī)格書可能導(dǎo)致運(yùn)放內(nèi)部寄生晶體管產(chǎn)生漏電流,從而導(dǎo)致芯片的輸出鉗位到正電源或者負(fù)電源���。

2. 不同的鉗位狀態(tài)可能導(dǎo)致同一電路出現(xiàn)不同表現(xiàn)�����,有些可以正常工作而有些不能���。

3. 運(yùn)放的鉗位狀態(tài)和芯片裸片(DIE)的layout有關(guān),即使是同一系列的運(yùn)放也可能有不同的layout從而導(dǎo)致不同的鉗位狀態(tài)���,因?yàn)樾酒闫膌ayout是不公開信息���,我們無法預(yù)知運(yùn)放的鉗位狀態(tài)。為了避免運(yùn)放因?yàn)檩斎氤?guī)格導(dǎo)致工作異常��,我們可以在輸入端對正負(fù)電源加鉗位二極管�,避免運(yùn)放輸入超規(guī)格,從而保證電路的正常工作���。

References

[1]. LM358 DATASHEET (SLOS068X)

[2]. Latch-Up, ESD, and Other Phenomena (SLYA014A)

推薦閱讀: