【導(dǎo)讀】自1971年至1986年期間, 國外發(fā)射的39顆同步衛(wèi)星因各種原因造成的故障共計1 589 次, 其中與空間輻射有關(guān)的故障有1 129次, 占故障總數(shù)的71%, 由此可見衛(wèi)星和航天器的故障主要來源于空間輻射。

1 抗輻照分析

空間輻照環(huán)境中的帶電粒子會導(dǎo)致星載電子設(shè)備工作異常和器件的失效, 嚴(yán)重影響航天器的可靠性和壽命。星載電子設(shè)備在工作期間所遇到的輻照問題主要是受到空間高能粒子(重離子和質(zhì)子)的影響。

1.1 總劑量效應(yīng)

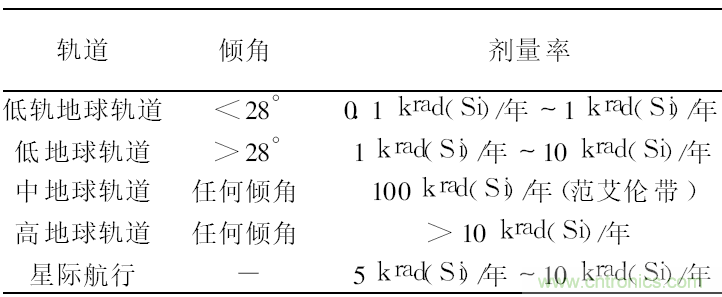

總劑量效應(yīng)指在電子器件的特性(電流、電壓門限值、轉(zhuǎn)換時間)發(fā)生重大變化前, 器件所能承受的總吸收能量級, 超過這個能量級后器件就不能正常工作(出現(xiàn)永久故障)。該劑量用Rad(Si)即存積在1 gSi中的能量來度量。典型軌道預(yù)計輻射量見表1??倓┝啃?yīng)會引起星上電子器件的物理效應(yīng)和電器效應(yīng)如產(chǎn)生電子空穴對、影響載流子的流動、對雙極型器件會降低其增益, 對CMOS器件會使其閾值電壓漂移、降低轉(zhuǎn)換速率等[ 1] 。

另外在對某星載雷達(dá)所用CMOS器件進(jìn)行總劑量實驗時發(fā)現(xiàn), 總劑量效應(yīng)在器件斷電后會有一定的退火現(xiàn)象, 但如果再加大輻射劑量, 退火后的器件很快就不能工作。

表1 幾種典型軌道預(yù)計輻射劑量

所以對長壽命、高可靠的星載電子設(shè)備, 必須考慮元器件的在軌期間的總劑量問題。對于總劑量效應(yīng)的防護(hù)可采用如下2種方法。

(1)選擇半導(dǎo)體工藝:選擇對宇宙射線不敏感的材料, CMOS藍(lán)寶石硅片(SOS)工藝是目前最合適的工藝, 但其成本高于其工藝。

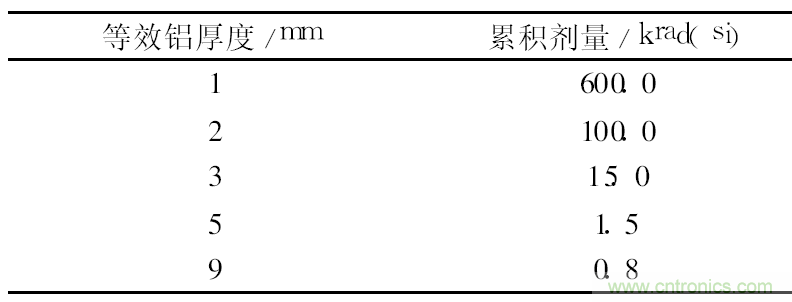

(2)輻射屏蔽:衛(wèi)星的結(jié)構(gòu)框架以及電子設(shè)備的外殼的屏蔽作用可減輕輻射的影響, 一般可減少2 krad~ 3 krad。表2是屏蔽外殼等效鋁厚度與累積劑量。因為屏蔽材料本身有2 次輻射, 所以它并不能有效地防護(hù)高能粒子(宇宙射線)產(chǎn)生的影響。

表2 等效鋁厚度與累積劑量

1.2 單粒子效應(yīng)

空間輻照環(huán)境使星載電子器件產(chǎn)生單粒子現(xiàn)象(SEP)。隨著電子器件集成度不斷提高, 器件尺寸不斷減小, 星載電子設(shè)備也變得更加復(fù)雜, 電子系統(tǒng)更易受到瞬態(tài)干擾, 因此在星載電子系統(tǒng)的設(shè)計過程中不僅要考慮輻射總劑量的影響同時也要研究高能粒子引起的單粒子現(xiàn)象。由分析可知單粒子(包括重離子、α粒子和中子等)引起的故障主要有瞬間故障、軟故障和永久損壞這3種。

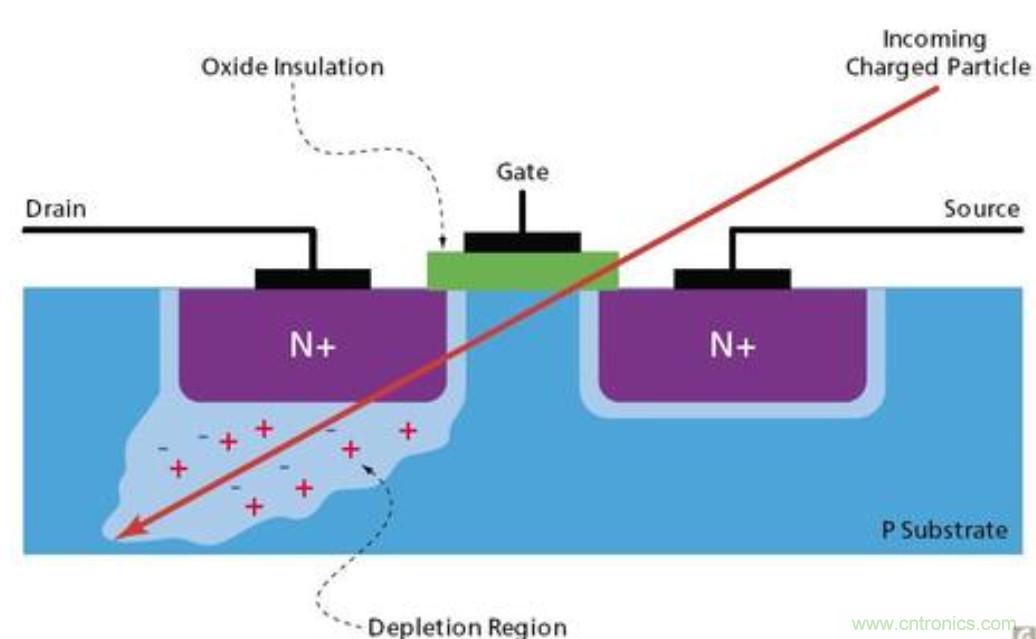

瞬態(tài)故障是輻照對內(nèi)部電子線路短時間的干擾,在一個時鐘周期內(nèi)可自行恢復(fù), 除故障瞬間一般不會造成電路的輸出錯誤。典型的瞬態(tài)故障是單粒子翻轉(zhuǎn)(SEU)效應(yīng), SEU是由高能單粒子離子化引起的。當(dāng)輻射離子通過器件時損失的能量通過線性傳遞給器件材料形成空穴-電子對, 進(jìn)而改變電路中某一節(jié)點的電平造成了雙穩(wěn)態(tài)器件狀態(tài)的暫時改變。有關(guān)數(shù)據(jù)顯示SEU的瞬態(tài)故障率大約為永久故障率的1 000倍[ 2] , 為降低這一風(fēng)險通常采取以下2種措施:

(1)對電子器件進(jìn)行加固防護(hù)或選用對電離離子不敏感的器件。從實驗可知單個器件對SEU的敏感性變化很大,最耐受SEU的工藝依次為CMOS/SOS、體硅CMOS、NMOS/I2L、TTL[ 3] 。

(2)采用可以允許SEU瞬態(tài)故障的方法設(shè)計硬件和軟件, 即設(shè)計具有容錯性的系統(tǒng)。

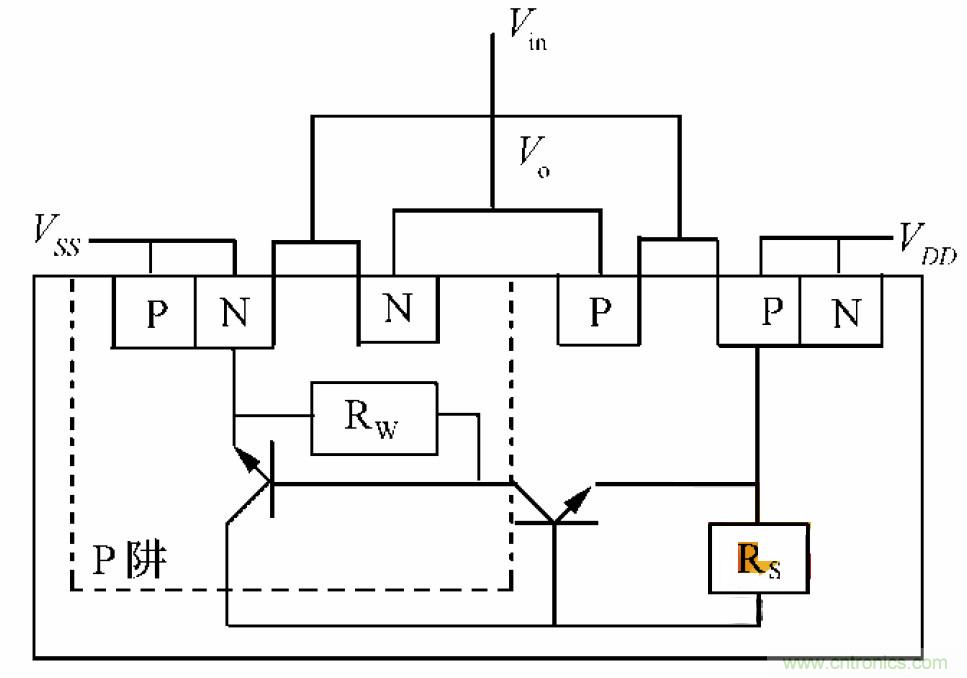

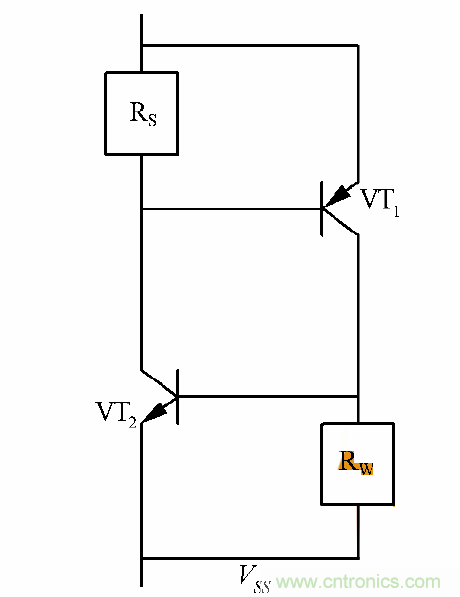

SEU屬于軟故障, 沒有對設(shè)備器件造成實質(zhì)性的損壞, 但單粒子閂鎖(SEL)很可能對器件造成不能立即修復(fù)的實質(zhì)性損壞, 即永久損壞。所以在電路設(shè)計中必須重視SEL的分析與防護(hù)。單粒子閂鎖主要發(fā)生在CMOS器件中, CMOS器件的主要優(yōu)點是功耗電流小, 正好適應(yīng)航天器件的要求, 因此CMOS器件大量應(yīng)用于星載電子設(shè)備中。所謂閂鎖就是指CMOS器件中固有的可控硅結(jié)構(gòu)被觸發(fā)導(dǎo)通, 在電源和地之間形成低電阻大電流的現(xiàn)象[ 4] 。如圖1所示, 以可編程門陣列(FPGA)的主要微電子器件CMOS反相器為例, 正常工作時2個寄生三極管均處于零偏, 即截止?fàn)顟B(tài), 對CMOS工作無影響。但在輻照環(huán)境下高能粒子作用于電源VDD端, 形成觸發(fā)電流, 若在寄生電阻RS上產(chǎn)生的壓降達(dá)到了VT1管的正向?qū)▔航祫tVT1 導(dǎo)通, 而集電極電流IC1則通過串聯(lián)電阻RW 流入VSS, 如果在RW 上產(chǎn)生的壓降也達(dá)到了VT2 的導(dǎo)通電壓, VT2 也會導(dǎo)通, 同時由于VT2的導(dǎo)通又加大了流過RS的電流導(dǎo)致VT1 管基極電位下降, 使得VT2 集電極電流進(jìn)一步增加, 從而形成了正反饋回路即發(fā)生了閂鎖, 如圖2所示。

圖1 CMOS反相器寄生PNPN結(jié)構(gòu)

圖2 寄生雙極晶體管等效電路

閂鎖一旦發(fā)生, 維持閂鎖只需要很低的電壓, 斷開輸入信號也不能恢復(fù)正常狀態(tài), 從閂鎖的形成機理來看, 防止或避免閂鎖造成的損壞主要有以下措施[ 5] :

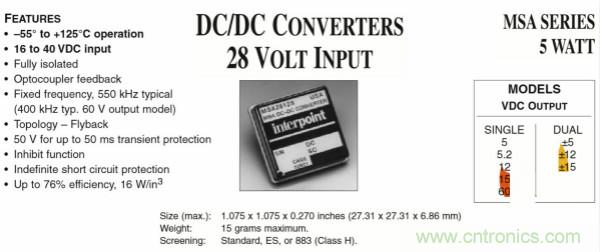

(1)使用帶有保護(hù)措施的電源模塊。例如Interpoint公司生產(chǎn)的電源轉(zhuǎn)換模塊MSA2805S可把28 V的電壓值轉(zhuǎn)換成電路使用的5 V電壓值, 該芯片在瞬時大電流的情況下能在短時間內(nèi)停止電壓轉(zhuǎn)換, 停止對設(shè)備供電, 過后可自行恢復(fù)。

(2)使用限流保護(hù)芯片。MIC5201 是航天設(shè)備中經(jīng)常使用的限流保護(hù)組件, 在出現(xiàn)正回饋時該芯片把電流限定在一定范圍之內(nèi), 可以防止瞬時大電流造成的破壞。

(3)熔絲電阻的使用。不同于一般的熔絲, 當(dāng)出現(xiàn)大電流時熔絲電阻2端的電阻變的無窮大即相當(dāng)于開路, 當(dāng)電路恢復(fù)正常時熔絲電阻兩端電阻又恢復(fù)成原先的阻值。

總之使用CMOS電路時防閂鎖的基本方法是確保輸入或輸出電平不會降到比VDD還低, 或升到比VSS還高。在發(fā)生閂鎖的情況下最可靠的方法是立即停止對設(shè)備供電。

1.3 靜電累積-放電效應(yīng)

空間輻射環(huán)境使航天器充電到高電位, 并導(dǎo)致航天器發(fā)生故障。靜電放電(ESD)是2個具有不同電位(由靜電引起)物體之間的電流流動。ESD會引起半導(dǎo)體器件的損傷, 使器件立即失效的幾率約10%(短路、開路、無功能、參數(shù)發(fā)生變化), 而90%的器件則會引入潛在損傷, 損傷后電參數(shù)仍符合規(guī)定要求但減弱了器件的抗過電應(yīng)力能力, 影響了器件的可靠性。通常ESD可引起2種失效模式:

(1)突發(fā)性完全失效;

(2)潛在性失效。

突發(fā)性完全失效是一個或多個電參數(shù)突然劣化完全失去規(guī)定功能的一種失效。對結(jié)型器件損傷往往導(dǎo)致PN結(jié)嚴(yán)重漏電和電流增益顯著下降;對CMOS電路由于存在寄生的可控硅效應(yīng), 靜電放電可能觸發(fā)閂鎖, 若供電回路無限流電阻存在, 器件易被過大電流燒毀。如果靜電能量較低或ESD回路中有限流電阻存在, 一次ESD脈沖不足以引起器件發(fā)射突發(fā)性失效, 但是會在器件內(nèi)部造成輕微的損傷,這種損傷是積累的, 隨著ESD脈沖數(shù)的增加器件的損傷閾值電壓會逐漸下降, 器件的電參數(shù)逐步劣化。這類失效稱為潛在性失效, 它降低了器件的抗靜電能力,降低了器件的可靠性。

一個良好的電子系統(tǒng)設(shè)備, 應(yīng)該在結(jié)構(gòu)設(shè)計和電路設(shè)計的最初階段就考慮瞬態(tài)保護(hù)問題。從電子設(shè)備的結(jié)構(gòu)設(shè)計和電路設(shè)計角度來講靜電防護(hù)方法主要有以下5種。

(1)屏蔽機箱。利用金屬機箱和屏蔽罩可以限制放電電流在機箱的外表面, 阻止靜電放電電弧以及相應(yīng)的電磁場, 并且保護(hù)設(shè)備免受間接放電的影響, 目的是將全部靜電阻隔在機箱之外。

(2)搭接。搭接的目的在于為靜電放電電流提供一個均勻的結(jié)構(gòu)面和低阻抗通路以避免在相互連接的2金屬件之間形成電位差。對于金屬機箱, 若機箱2部分之間的搭接阻抗較高, 靜電放電電流就會在搭接點形成較高的壓降, 如果搭接電阻為0.1 Ψ, 放電電流為30 A時, 則會產(chǎn)生3 V的電壓。如果電路利用這個機箱作為公共地, 則意味著不同電路的參考電位相差3V, 影響系統(tǒng)工作的穩(wěn)定性。

(3)信號地機箱單點連接。如果電路與機箱連在一起, 就只應(yīng)通過一點連接, 可防止放電電流流過電路。否則機箱上的電流會流進(jìn)電路, 造成干擾。信號地與機箱連接起來的另一個目的是當(dāng)機箱上發(fā)生靜電放電時, 機箱的電位升高, 由于線路板與機箱連接在一起, 保證電路板的電位也同時升高, 從而防止了線路板與機箱之間的二次放電。

(4)電纜設(shè)計。良好的電纜保護(hù)設(shè)計可以提高系統(tǒng)抗ESD干擾的能力, 為減小輻射EMI耦合到電纜,應(yīng)盡量縮短線長且盡量采用屏蔽電纜。若2個機箱需要電纜互聯(lián)時, 電纜的屏蔽層要和2個機箱相連, 這樣可以使兩個機箱等電位, 防止產(chǎn)生電位差。

(5)PCB設(shè)計。印制電路板對靜電放電電流產(chǎn)生的磁場非常敏感, 所以印制電路板上所有回路的面積都應(yīng)盡可能小, 可以通過使用多層板及地線網(wǎng)格減小回路面積。其次電路板上的布線也是抗瞬態(tài)沖擊的重要方面。走線上的寄生電感對于瞬態(tài)沖擊會產(chǎn)生電壓尖峰, 量級可能會超過芯片引腳的極限值。因此, 設(shè)計時, 須努力減小被保護(hù)信號線及信號回路上的寄生電感。布線時盡量縮短引線長度、加大線寬等。

關(guān)于靜電放電對于CMOS電路的危害, 由于主要是引起閂鎖效應(yīng), 所以其電路的靜電防護(hù)設(shè)計可參考上文中關(guān)于閂鎖的防護(hù)措施。

2 航天電子器件的選用

按照國際通用的分類方法, 電子元器件等級一般可分為宇航級或883B級、軍級、工業(yè)級、商業(yè)級[ 6] ??臻g電子產(chǎn)品設(shè)計時對元器件的選用有2種途徑:

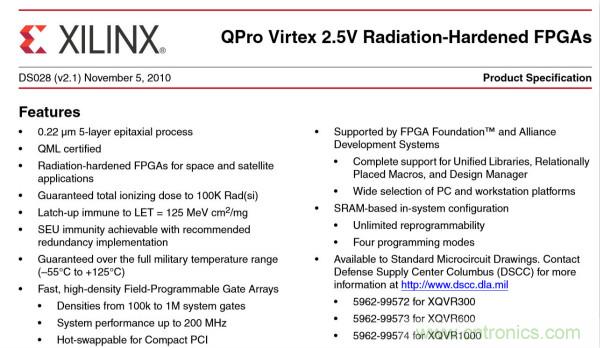

(1)采用抗輻射加固器件。優(yōu)先選擇有抗輻射加固、可靠性高、抗輻射能力強的宇航級器件或采用抗輻射加固后的883B級器件。目前國外FPGA廠商已經(jīng)可以生產(chǎn)大容量的抗輻照FPGA。如Xilinx公司的QPro-R航天抗輻照系列FPGA, 最大容量達(dá)600萬門;

Actel公司的RTAX4000 系列航天抗輻照FPGA最大容量達(dá)400萬門。這些大容量抗輻照FPGA的推出推動了星載電子設(shè)備小型化的發(fā)展。

(2)采用商用器件。在沒有可供選擇的宇航級或883B級器件情況下, 或為了滿足系統(tǒng)的高性能要求, 可以有控制地使用商用器件。

對商業(yè)級器件一般可做如下加固處理:

(1)利用衛(wèi)星蒙皮、設(shè)備機箱、加局部屏蔽的方法提高器件的抗輻射水平。

(2)在設(shè)計時采用多機容錯、電路冗余設(shè)計、冷熱備份來提高整機抗輻射水平。

(3)多機容錯、電路冗余設(shè)計、輪換工作、冷熱備份等提高整機抗輻射水平。

(4)商用器件必須經(jīng)過篩選測試:采取特定的針對商用器件的篩選測試, 剔除具有早期失效危險和固有缺陷的器件, 提高器件的可靠性。

高性能商用器件的空間應(yīng)用在國際上已經(jīng)成為一種發(fā)展趨勢, 近些年來, 國內(nèi)也逐步開始了商用器件空間應(yīng)用的探索。中國科學(xué)院空間科學(xué)與應(yīng)用研究中心近年來在載人航天工程和雙星計劃等航天任務(wù)中曾采用了幾種商用器件, 并取得了在軌飛行的成功經(jīng)驗。

2003年12月31日和2004年7月25日發(fā)射的雙星探測一號衛(wèi)星和探測二號衛(wèi)星中, 有效載荷數(shù)據(jù)管理系統(tǒng)載荷配電器采用了商用塑封器件高端電流檢測芯MAX471EPA, 均獲得在軌運行的圓滿成功。

3 結(jié)束語

抗輻照分析對于星載電子設(shè)備的設(shè)計至關(guān)重要,必須根據(jù)設(shè)備所處的具體空間輻射環(huán)境, 提出系統(tǒng)總體抗輻射加固要求, 并分配給單機、器件, 進(jìn)行系統(tǒng)級加固設(shè)計;然后進(jìn)行單機抗輻射設(shè)計, 并根據(jù)抗輻射設(shè)計要求設(shè)計具有抗輻射性能的電路;最后按照需要選擇元器件。空間輻照環(huán)境是變化、復(fù)雜的, 需進(jìn)一步掌握空間環(huán)境對電子設(shè)備的影響, 使其適應(yīng)空間環(huán)境, 長期、可靠的工作。

推薦閱讀: