【導(dǎo)讀】對(duì)于需要一系列同步模數(shù)轉(zhuǎn)換器(ADC)的高速信號(hào)采樣和處理應(yīng)用,解偏斜和轉(zhuǎn)換器的延遲變化匹配是至關(guān)重要的。圍繞該特性展開(kāi)的系統(tǒng)設(shè)計(jì)極為關(guān)鍵�,因?yàn)閺哪M采樣點(diǎn)到處理模塊之間的任何延遲失配都會(huì)使性能下降�。對(duì)于交錯(cuò)式處理而言�����,樣本對(duì)齊同樣是必需的�;在交錯(cuò)式處理時(shí)�,一個(gè)轉(zhuǎn)換器樣本后緊跟另一個(gè)樣本,且時(shí)間僅為一個(gè)時(shí)鐘周期中的一小部分�。

JESD204B 第三代高速串行轉(zhuǎn)換器接口的一個(gè)重要特性,是其能夠確立系統(tǒng)中每個(gè)轉(zhuǎn)換器的確定性延遲��。正確理解并利用該特性�����,便可在單系統(tǒng)中針對(duì)多個(gè)ADC創(chuàng)建同步或交錯(cuò)采樣系統(tǒng)��。

由于確定性延遲是相對(duì)較新的轉(zhuǎn)換器接口特性��,系統(tǒng)設(shè)計(jì)人員經(jīng)常就如何建立��、目標(biāo)信號(hào)以及如何部署為同步或交錯(cuò)式處理等方面存有諸多疑問(wèn)�����。下文的部分常見(jiàn)問(wèn)題與解答針對(duì)多個(gè)與FPGA一同采樣的JESD204B轉(zhuǎn)換器并使用確定性延遲進(jìn)行系統(tǒng)設(shè)計(jì)而言。

什么是確定性延遲�,它在JESD204B中是如何定義的?

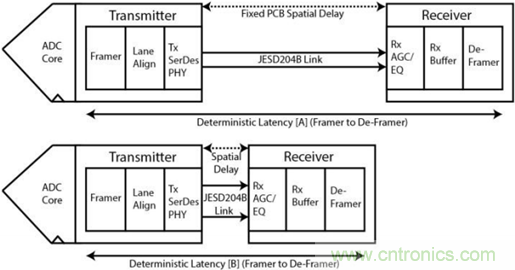

JESD204B鏈路的確定性延遲定義為串行數(shù)據(jù)從發(fā)送器(ADC或源端FPGA)的并行幀數(shù)據(jù)輸入傳播至接收器(DAC或接收端FPGA)并行去幀數(shù)據(jù)輸出所需的時(shí)間��。該時(shí)間通常以分辨率為幀時(shí)鐘周期或以器件時(shí)鐘進(jìn)行測(cè)量�。

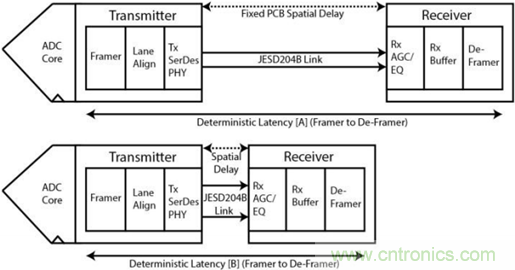

JESD204B的確定性延遲規(guī)格沒(méi)有考慮到ADC模擬前端內(nèi)核或DAC后端模擬內(nèi)核的情況�����。它只基于輸入和輸出JESD204B數(shù)字幀的數(shù)據(jù)��。不僅兩個(gè)有源器件在這種延遲計(jì)算中作為函數(shù)使用��,與兩個(gè)器件接口的空間信號(hào)路由也將作為函數(shù)參與計(jì)算�����。這意味著每條鏈路的確定性延遲在多轉(zhuǎn)換器系統(tǒng)中��,可能較大或較小�����,具體取決于JESD204B通道的路由長(zhǎng)度及其各自的延遲情況��。接收器的緩沖器延遲有助于彌補(bǔ)路由造成的延遲差異(圖1)。

圖1.兩個(gè)JESD204B器件之間的確定性延遲取決于三方面:發(fā)送器成幀器到輸出端的延遲�、空間路由延遲和輸入端到解幀器的接收器延遲。來(lái)自同一個(gè)系統(tǒng)中兩個(gè)不同ADC的數(shù)據(jù)可能各自具有獨(dú)特的確定性延遲�����。

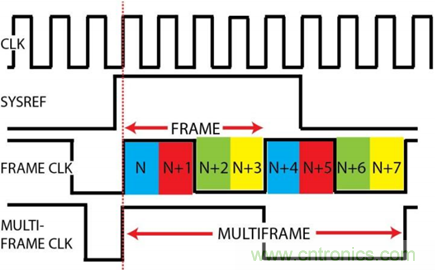

與簡(jiǎn)單的串行鏈路配置不同——比如低壓差分信號(hào)(LVDS)——JESD204B接口將數(shù)據(jù)樣本打包為定義幀�。幾個(gè)或多個(gè)樣本的每一個(gè)幀邊界在鏈路握手或初始通道對(duì)齊序列(ILAS)階段均由來(lái)自發(fā)送器的特殊控制字符標(biāo)記。更大的已定義幀群——稱為多幀——在ILAS階段同樣采用相應(yīng)的控制字符標(biāo)記�。然而,該序列完成后��,便不再需要控制字符��,并且可以獲取鏈路的全帶寬��。幀邊界和多幀邊界分別與幀時(shí)鐘和多幀時(shí)鐘重合�。

JESD204B子類與確定性延遲的關(guān)系意味著什么?

JESD204B協(xié)議的三個(gè)子類定義了鏈路的確定性延遲��。子類0向后兼容JESD204 和JESD204A�����,不支持確定性延遲�。子類1通 過(guò)稱為SYSREF的系統(tǒng)參考信號(hào)支持確定性延遲�����。子類2通過(guò)對(duì)~SYNC信號(hào)的雙重使用支持確定性延遲�,并同樣允許接收器初始化握手ILAS例程��。精確將SYSREF與~SYNC以相對(duì)于時(shí)鐘的時(shí)間關(guān)系對(duì)齊的能力表明目標(biāo)系統(tǒng)所需的子類�����。

確定性延遲如何用作多個(gè)轉(zhuǎn)換器的采樣對(duì)齊�����?

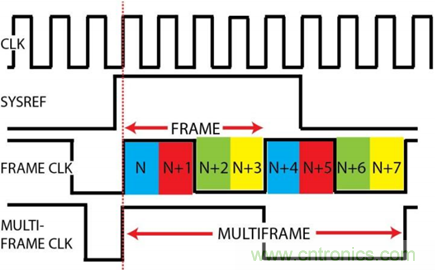

對(duì)于子類1而言��,幀時(shí)鐘和多幀時(shí)鐘將于出現(xiàn)系統(tǒng)參考邊沿(SYSREF)時(shí)在每個(gè)器件內(nèi)部對(duì)齊�。檢測(cè)到SYSREF邊沿時(shí)�����,這些時(shí)鐘與該點(diǎn)時(shí)間對(duì)齊�。由于這些時(shí)鐘對(duì)每個(gè)器件而言都是內(nèi)部的,它們?cè)诎l(fā)送器內(nèi)的邊界可利用控制字符通過(guò)串行鏈路通信��。

每個(gè)接收器相對(duì)其自身時(shí)鐘——這些時(shí)鐘具有相同的名稱——并相對(duì)所有發(fā)送器間接解碼發(fā)送器幀和多幀時(shí)鐘位置。這使得接收器可以解偏斜相對(duì)較早到達(dá)的數(shù)據(jù)樣本�,從而利用緩沖器延遲,以最后到達(dá)的數(shù)據(jù)匹配鏈路(圖2)�����。

圖2.在JESD204B發(fā)送器內(nèi)��,樣本于時(shí)鐘鎖存系統(tǒng)參考(SYSREF)邊沿后對(duì)齊幀和多幀時(shí)鐘�����。為直觀起見(jiàn)�����,本文定義的多幀僅由8個(gè)樣本組成�。

對(duì)于同步采樣而言,這些數(shù)據(jù)鏈路可在FPGA內(nèi)按時(shí)間排列��。對(duì)于交錯(cuò)采樣而言�����,每個(gè)鏈路都能以其對(duì)應(yīng)的相對(duì)相位延遲進(jìn)行偏置��。確定性延遲可通過(guò)按時(shí)間對(duì)每個(gè)鏈路進(jìn)行測(cè)量而加以識(shí)別,即從接收器多幀時(shí)鐘邊沿到每個(gè)對(duì)應(yīng)鏈路的多幀控制字符�����。此處需注意��,每個(gè)鏈路的確定性延遲必須不能超過(guò)一個(gè)多幀時(shí)鐘周期(圖3)�。

圖3.利用緩沖器延遲,來(lái)自JESD204B發(fā)送器并以多幀形式出現(xiàn)的樣本能與多幀時(shí)鐘對(duì)齊��。

確定性延遲是否等同于總轉(zhuǎn)換器延遲�����?

ADC的總延遲表示其輸入一個(gè)模擬樣本��、處理�����、并從器件輸出數(shù)字信號(hào)所需的時(shí)間��。類似地��,DAC的總延遲表示從數(shù)字樣本數(shù)據(jù)輸入器件直到模擬輸出相應(yīng)樣本的時(shí)間�����。通常��,對(duì)這兩者都以分辨率為采樣時(shí)鐘周期進(jìn)行測(cè)量�,因?yàn)樗鼈兣c頻率有關(guān)。它與單個(gè)轉(zhuǎn)換器元件內(nèi)的模擬處理架構(gòu)部分相關(guān)�。這在原理上與JESD204B鏈路部署中描述的確定性延遲的定義有所不同;該定義表明其與三個(gè)元件有關(guān)��。

對(duì)齊多個(gè)轉(zhuǎn)換器的解偏斜預(yù)算最大是多少�?

在ILAS處理階段,發(fā)送器發(fā)送多幀控制字符��,標(biāo)記多幀時(shí)鐘邊界�。接收器識(shí)別這些字符,并創(chuàng)建自有局部多幀時(shí)鐘�����,與上游鏈路的所有發(fā)送器對(duì)齊�。對(duì)于采用多個(gè)接收器的大型陣列系統(tǒng),多幀時(shí)鐘同樣需在所有這些器件中對(duì)齊��。因此�,任意轉(zhuǎn)換器鏈路的確定性延遲都不可超過(guò)單個(gè)多幀時(shí)鐘周期�����。這是鏈路上的總偏斜時(shí)間預(yù)算�����。

多幀時(shí)鐘的持續(xù)時(shí)間通常為采樣時(shí)鐘周期的數(shù)十倍�。它甚至還能通過(guò)設(shè)置參數(shù)變量��,在鏈路握手期間調(diào)節(jié)為更長(zhǎng)或更短��。

該特性能否在ADC或DAC上正確對(duì)齊至同樣的模擬采樣點(diǎn)�����?有沒(méi)有其它要求�?

確定性延遲按照以JESD204B成幀器時(shí)間為順序的時(shí)間點(diǎn),提供樣本對(duì)齊方式��。除此時(shí)間之外�����,ADC還將具有更多延遲時(shí)鐘周期�����,可用來(lái)處理來(lái)自JESD204B成幀器以前的前端模擬樣本��。轉(zhuǎn)換器供應(yīng)商必須指定該時(shí)間周期位于成幀器之前��,長(zhǎng)度為時(shí)鐘長(zhǎng)度��。相反��,解幀器處理樣本并以模擬形式輸出后�����,DAC將需要額外的時(shí)鐘周期�����。

在有效模擬樣本數(shù)據(jù)可用以前��,對(duì)齊過(guò)程需多長(zhǎng)時(shí)間��?

SYSREF邊沿發(fā)送至轉(zhuǎn)換器和FPGA��,開(kāi)啟對(duì)齊過(guò)程。此事件后�����,需要完成多個(gè)多幀時(shí)鐘周期以及ILAS序列��,才能獲取有效樣本數(shù)據(jù)�����。這與許多采樣時(shí)鐘周期的相對(duì)時(shí)間等效�����。特定的持續(xù)時(shí)間可能取決于轉(zhuǎn)換器內(nèi)部的JESD204B內(nèi)核特有確定性延遲��,該數(shù)據(jù)由供應(yīng)商提供��。在該時(shí)間內(nèi)�����,鏈路關(guān)斷�����,不傳輸有效數(shù)據(jù)��。在絕對(duì)時(shí)間內(nèi)�,持續(xù)時(shí)間將是采樣時(shí)鐘頻率的函數(shù)。

對(duì)于系統(tǒng)設(shè)計(jì)而言��,實(shí)現(xiàn)同步采樣最大的挑戰(zhàn)在哪里�����?

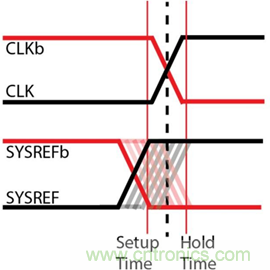

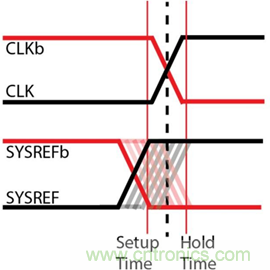

在子類1中�����,實(shí)現(xiàn)低至樣本級(jí)的同步或交錯(cuò)處理所遇到的最大挑戰(zhàn)之一�����,是在多個(gè)轉(zhuǎn)換器中按序?qū)RSYSREF的使能邊沿��。此外�,每個(gè)SYSREF邊沿都要滿足其對(duì)應(yīng)采樣時(shí)鐘的建立和保持時(shí)間要求。這將消耗一部分可用的時(shí)序裕量�����。主動(dòng)、獨(dú)立地偏斜SYSREF和時(shí)鐘之間的精細(xì)相位將有助于實(shí)現(xiàn)轉(zhuǎn)換器上的時(shí)序收斂�。

SYSREF是單次事件還是重復(fù)事件?每種情況下分別需要了解什么�����?

SYSREF對(duì)齊邊沿可以是單次脈沖�����、周期信號(hào)�、帶隙周期信號(hào)或重復(fù)非周期信號(hào)。它將根據(jù)系統(tǒng)的需要�,以及源端的時(shí)鐘與SYSREF之間的相位偏斜時(shí)序靈敏度而定。對(duì)于重復(fù)SYSREF信號(hào)而言�����,幀和多幀時(shí)鐘將在每次事件發(fā)生時(shí)重新對(duì)齊��。然而��,由于目標(biāo)是保持一組對(duì)齊的時(shí)鐘�����,重復(fù)周期SYSREF信號(hào)的使能邊沿應(yīng)當(dāng)在多幀時(shí)鐘邊界下降。由于時(shí)鐘應(yīng)當(dāng)已經(jīng)在第一個(gè)SYSREF邊沿后對(duì)齊��,因此這樣可以防止不必要的重復(fù)對(duì)齊��。

周期性SYSREF信號(hào)的一個(gè)不利影響�,就是可能會(huì)耦合至目標(biāo)模擬信號(hào)��。這便是為什么不建議始終采用周期信號(hào)的原因�;僅在萬(wàn)不得已時(shí)才使用周期信號(hào)。如果使用了周期性SYSREF�,則必須仔細(xì)地將其與ADC模擬前端正確隔離。

SYSREF偏斜調(diào)節(jié)至單時(shí)鐘周期以內(nèi)的方法有哪些��?

理想情況下��,用于每個(gè)轉(zhuǎn)換器和FPGA的SYSREF和時(shí)鐘可精確路由�����,其時(shí)序裕量滿足所有元件的苛刻建立時(shí)間和保持時(shí)間要求�。但隨著高性能轉(zhuǎn)換器的采樣速度不斷增長(zhǎng),僅通過(guò)精密印刷電路板(PCB)路由已無(wú)法始終滿足時(shí)序收斂要求�����。不同器件的引腳間差異以及電源和溫度偏差會(huì)在高速轉(zhuǎn)換器陣列上產(chǎn)生一個(gè)相對(duì)較大的時(shí)序偏斜?�?赡苄枰呒?jí)時(shí)序調(diào)節(jié)功能來(lái)提供主動(dòng)SYSREF相位偏斜�����。

例如��,來(lái)自ADC的警報(bào)可以識(shí)別SYSREF邊沿是否鎖存至建立時(shí)間并保持在阻擋時(shí)序窗口中��。如果確實(shí)如此�,那么對(duì)于哪個(gè)時(shí)鐘邊沿(時(shí)鐘[N]或時(shí)鐘[N+1])用于時(shí)序參考將存在不確定性。取決于何處檢測(cè)到SYSREF邊沿�����,相對(duì)于SYSREF的采樣CLK邊沿相位在時(shí)鐘源處可能存在延遲��,以保持有效時(shí)序條件�,滿足建立和保持時(shí)間要求。

另一種方法是利用采樣時(shí)鐘的下一個(gè)下降沿(而非上升沿)來(lái)獲取相位裕量的半周期�。系統(tǒng)中的所有轉(zhuǎn)換器均能以這種方式進(jìn)行調(diào)整,前提是時(shí)鐘源針對(duì)相應(yīng)的SYSREF和CLK具有獨(dú)立的相位調(diào)整(圖4)��。

圖4.如需在高速下達(dá)到低至樣本級(jí)的對(duì)齊性能��,則滿足相對(duì)于輸入時(shí)鐘的SYSREF建立-保持時(shí)間要求可能有難度。 在相位的早期階段(相對(duì)于CLK)偏斜每一個(gè)SYSREF輸入以防建立時(shí)間偏差的能力有助于滿足系統(tǒng)中多個(gè)轉(zhuǎn)換器的時(shí)序收斂要求��。

支持子類1和子類2的轉(zhuǎn)換器需要使用確定性延遲功能嗎�����?

如JESD204B規(guī)格定義�����,子類1和子類2是僅有支持確定性延遲的子類��。在子類1中�,SYSREF信號(hào)定義確定性延遲�。在子類2中,~SYNC信號(hào)定義該延遲��。然而�����,某些轉(zhuǎn)換器供應(yīng)商創(chuàng)建了子類0部署��,用來(lái)支持樣本對(duì)齊的同步方案�����。這種情況下,不使用轉(zhuǎn)換器和FPGA之間的多幀時(shí)鐘對(duì)齊步驟��。

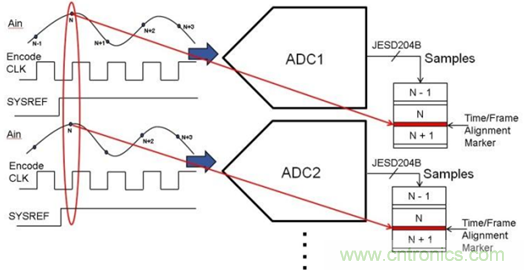

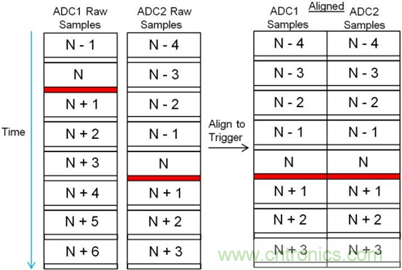

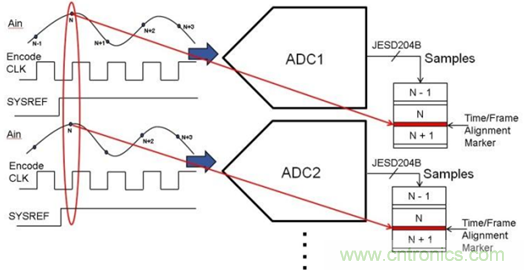

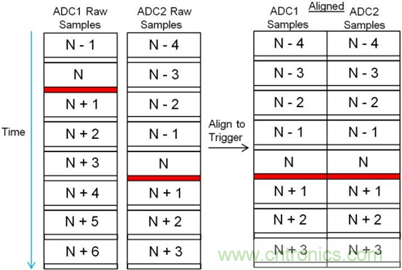

利用附加的輔助信息(稱為控制位)��,可在樣本級(jí)采用時(shí)間戳機(jī)制標(biāo)記SYSREF的出現(xiàn)情況�。與SYSREF邊沿重合的每一個(gè)樣本均以唯一控制位標(biāo)記。在FPGA內(nèi)�,所有擁有此時(shí)間戳的鏈路可以延遲至等于最長(zhǎng)路徑然后互相對(duì)齊,與轉(zhuǎn)換器之間的延遲差別無(wú)關(guān)(圖5和圖6)��。

圖5.利用SYSREF控制位時(shí)間戳��,在一個(gè)FPGA處理模塊內(nèi)可實(shí)現(xiàn)子類0中的樣本對(duì)齊�,而與模擬輸入到JESD204B輸出之間多個(gè)ADC上的實(shí)際延遲差異無(wú)關(guān)。

圖6.利用附加的控制位作為觸發(fā)器(紅色�,標(biāo)記為與前端模擬輸入重合),則FPGA可以對(duì)齊具有不同延遲的信號(hào)鏈樣本�。

小結(jié)

雖然確定性延遲是JESD204B中較為復(fù)雜的一項(xiàng)特性,但若善加利用便可成為高性能信號(hào)處理系統(tǒng)設(shè)計(jì)中的一項(xiàng)強(qiáng)大特性�����。來(lái)自ADC陣列的樣本可通過(guò)緩沖器延遲在FPGA內(nèi)部對(duì)齊并解偏斜�,從而實(shí)現(xiàn)同步或交錯(cuò)采樣��。JESD204B子類識(shí)別對(duì)于理解系統(tǒng)的時(shí)序?qū)R能力非常重要�����。時(shí)序收斂于SYSREF以及系統(tǒng)ADC的CLK輸入引腳對(duì)于實(shí)現(xiàn)樣本的時(shí)間對(duì)齊而言極為關(guān)鍵�����。

本文轉(zhuǎn)載自亞德諾半導(dǎo)體�����。

推薦閱讀: