【導(dǎo)讀】C2000系列芯片在數(shù)字電源和電機(jī)控制中有著廣泛的應(yīng)用���,在這些應(yīng)用中���,過(guò)流過(guò)壓保護(hù)是必不可少的��。TI 的Picollo系列芯片從F2802x開(kāi)始���,就已經(jīng)集成了帶DAC的片內(nèi)比較器��,通過(guò)DAC設(shè)定閾值���,與采樣信號(hào)分別送到片內(nèi)比較器的正負(fù)輸入端做比較,生成保護(hù)信號(hào)給到PWM模塊封鎖PWM輸出���,從而實(shí)現(xiàn)過(guò)流過(guò)壓保護(hù)��,響應(yīng)速度快���,無(wú)需額外再加比較器和基準(zhǔn)電壓。

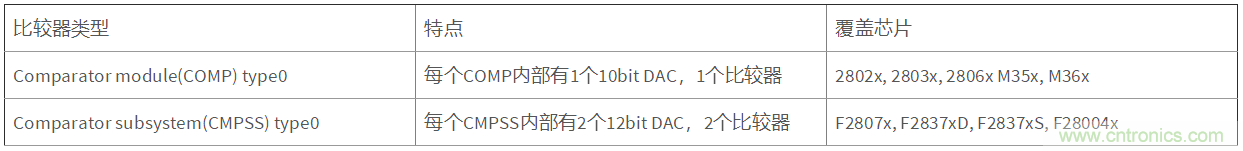

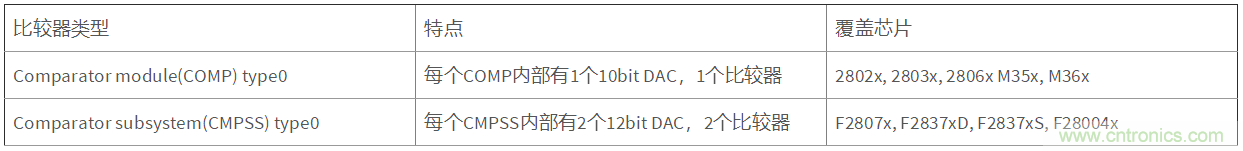

C2000系列芯片的內(nèi)置比較器主要可以分為如下兩類:

不管是以上哪種類型的比較器���,其輸入正端都是直接連到ADC采樣口(這個(gè)口用來(lái)采樣需要監(jiān)控的信息比如電壓或電流)���,輸入負(fù)端則可以選擇連到內(nèi)部的DAC輸出或者另一個(gè)ADC采樣口���。本文將以比較器負(fù)端連到內(nèi)部DAC輸出為例(這也是最常見(jiàn)的一種用法),介紹內(nèi)部比較器可能的誤差來(lái)源及其矯正方法���。

誤差來(lái)源:

1. static offset error��,靜態(tài)失調(diào)誤差���。

2. 比較器滯環(huán)

3. ADC基準(zhǔn)和比較器內(nèi)部DAC基準(zhǔn)差異。

一��、static offset error靜態(tài)失調(diào)誤差

現(xiàn)在假設(shè)我們希望的比較閾值為1.5V��,當(dāng)比較器正端輸入電壓大于1.5V時(shí)���,比較器輸出為1(高電平);輸入電壓小于1.5V時(shí)���,比較器輸出0(低電平)��。如果內(nèi)部DAC的基準(zhǔn)為3V���,那么我們需要把DACVAL設(shè)定為2048使得DAC輸出1.5V��。在上面描述的這種情況下有兩個(gè)地方會(huì)引入誤差��,一個(gè)是內(nèi)部DAC的誤差(offset error)��,另一個(gè)是比較器的誤差(input referred offset error)���,這兩個(gè)誤差總稱為static offset error,靜態(tài)失調(diào)誤差���。

對(duì)于F28004x��, F2807x��,F(xiàn)2837x系列芯片��,其規(guī)格書上都有static offset error這個(gè)參數(shù)��,為±25mV���。也就是說(shuō),雖然理論上DACVAL=2048可以得到1.5V的閾值���,但是因?yàn)閟tatic offset error���,比較器發(fā)生翻轉(zhuǎn)時(shí)負(fù)端的電壓可能在1.475V到1.525V之間���,而這個(gè)值是多少你并不知道,所以就需要校準(zhǔn)���。校準(zhǔn)方法就是��,在比較器正端接上一個(gè)你需要的閾值電平��,在關(guān)掉內(nèi)部比較器滯環(huán)的條件下���,讓比較器的DACVAL從0逐漸增大到4095,再逐漸減小到0���,這樣比較器輸出會(huì)有兩次翻轉(zhuǎn),將這兩次翻轉(zhuǎn)時(shí)的DACVAL的值作平均���,就是校正后的閾值電壓對(duì)應(yīng)的DACVAL的值���。

如果不用內(nèi)部的DAC生成比較閾值��,比較器的正端和負(fù)端都接外部信號(hào)的話��,那么就只需要考慮比較器的誤差了��。

二��、比較器滯環(huán)

C2000比較器的滯環(huán)是可以設(shè)定的��,COMPHYSCTL的COMPHYS位可以設(shè)定滯環(huán)的環(huán)寬���,當(dāng)環(huán)寬設(shè)定為0時(shí)也就意味著沒(méi)有滯環(huán)。注意在規(guī)格書中���,滯環(huán)的單位是LSB��,所以它和CMPSS模塊內(nèi)部的DAC的參考有關(guān)��。如果內(nèi)部DAC的參考電壓是3V���,1LSB對(duì)應(yīng)3V/4096=0.7mV。以F28004x��,F(xiàn)2807x, F2837x為例���,其滯環(huán)可以在12LSB, 24LSB, 36LSB, 48LSB中選擇���。

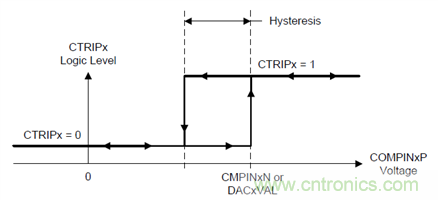

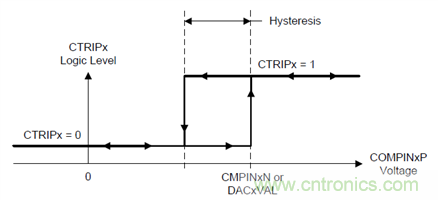

需要指出的是,加入滯環(huán)后���,比較器從0翻轉(zhuǎn)到1的閾值依然是之前校準(zhǔn)過(guò)的值��,而不會(huì)變成(校準(zhǔn)過(guò)的值+1/2*滯環(huán)寬度)��,而從1翻轉(zhuǎn)回0的閾值則會(huì)變成(校準(zhǔn)過(guò)的值-滯環(huán)寬度)���,如下圖所示:

三、ADC基準(zhǔn)和比較器內(nèi)部DAC基準(zhǔn)的差異

在實(shí)際系統(tǒng)中��,除了用比較器做硬件保護(hù)���,通過(guò)AD采樣來(lái)做軟件保護(hù)也很常見(jiàn)��。對(duì)于同一個(gè)電壓或者電流信號(hào)��,在考慮了前述靜態(tài)失調(diào)誤差和滯環(huán)后,有時(shí)候我們會(huì)發(fā)現(xiàn)ADC采樣得到的值根本沒(méi)到比較器DAC輸出的閾值���,但是比較器依然翻轉(zhuǎn)了��,這其中甚至?xí)畹?00個(gè)LSB��。這是因?yàn)樾酒珹DC的基準(zhǔn)電壓和比較器內(nèi)部DAC的基準(zhǔn)電壓不同導(dǎo)致的��。

以F28004x���,F(xiàn)2807x��, F2837x為例��,比較器內(nèi)部DAC的基準(zhǔn)默認(rèn)來(lái)自于VDDA���,可以配置成VDAC,而ADC的基準(zhǔn)來(lái)自于VREFHI��,VDDA默認(rèn)供電是3V���,而我們常用的內(nèi)部ADC基準(zhǔn)VREFHI是3.3V���,這樣,如果我們的比較器DACVAL設(shè)定為2048,那么比較器會(huì)在1.5V翻轉(zhuǎn)��,而此時(shí)ADC采樣的值只有1.5V/3.3V*4096=1862��。這就是因?yàn)锳DC基準(zhǔn)和比較器內(nèi)部DAC基準(zhǔn)的不同帶來(lái)的差異��,對(duì)于既需要做硬件保護(hù)���,又需要做軟件保護(hù)的信號(hào)���,這一點(diǎn)需要特別注意。最簡(jiǎn)便的解決辦法就是��,將比較器內(nèi)部的DAC基準(zhǔn)配置為VDAC���,同時(shí)將VDAC連到VREFHI上���,使得兩者的基準(zhǔn)一致。

結(jié)論

本文以F28004x���,F(xiàn)2807x���,F(xiàn)2837x芯片為例���,介紹了內(nèi)置比較器的誤差來(lái)源及校正方法,同時(shí)糾正了比較器滯環(huán)的錯(cuò)誤理解��。對(duì)于同一個(gè)信號(hào)既需要軟件保護(hù)又需要硬件保護(hù)的系統(tǒng)��,我們指出了導(dǎo)致軟硬件保護(hù)閾值可能出現(xiàn)偏差的原因��,同時(shí)給出了解決辦法���。正確使用C2000芯片內(nèi)部比較器可以實(shí)現(xiàn)快速軟硬件保護(hù),提高系統(tǒng)整體可靠性���,同時(shí)無(wú)需外部基準(zhǔn)和比較器���,節(jié)省PCB空間,是一個(gè)非常實(shí)用的模塊��。

推薦閱讀: