【導讀】在上一篇的文章中我們有截取各組信號的大致走線結構,從這個走線上我們到底可以看出什么問題會導致該DDR2系統(tǒng)運行異常呢?下面請看我們一一為您分解。

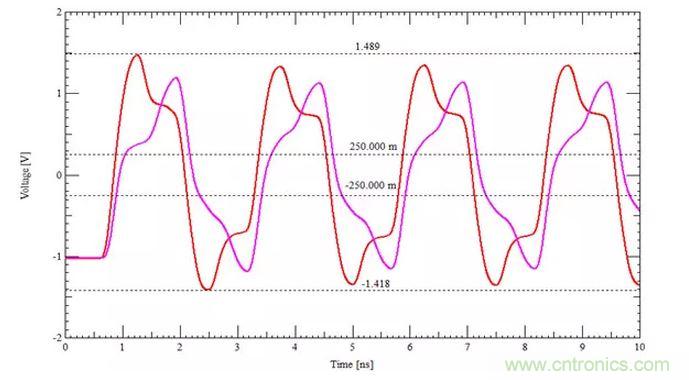

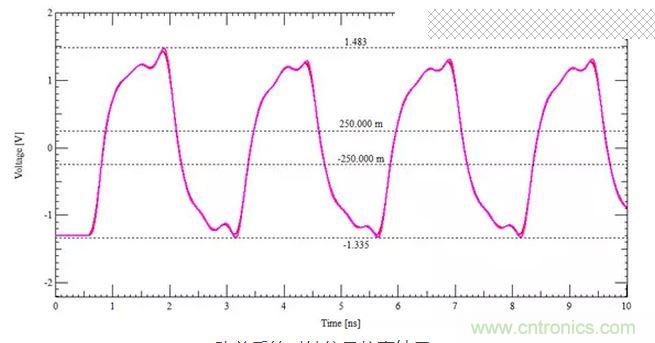

時鐘信號一拖二采用T型拓撲結構無可厚非,也說明有一定的設計概念,但是對于T型拓撲的設計要點還不是很清楚。一般我們的DDR2信號的T型結構需要主干線比較長,分支比較短,最好在500mil以內,這是看到的第一個問題,該設計分支和主干線路長度差不多;第二個問題是如果要外部端接,一般這個端接會放到第一個分支處,而該設計雖然在分支處加了端接,但在另一端靠近顆粒處又加了一個多余的端接,這就造成我們T型結構的不平衡。所謂的T型又叫等臂分支結構,需要兩個分支長度、結構、端接盡量一致(長度有偏差時,最好控制在20mil內),而該設計卻沒有做到這一點。我們仿真了原版本設計和改善后的時鐘信號,波形對比如下所示。

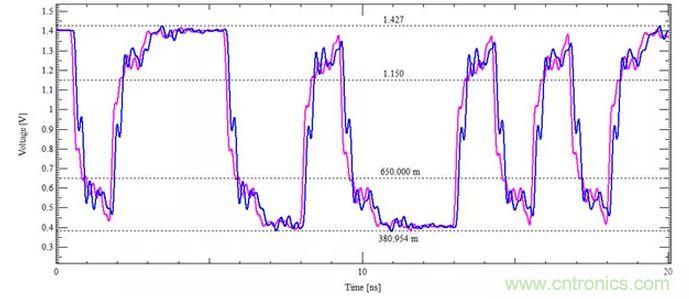

原始版本時鐘信號仿真結果

改善后的時鐘信號仿真結果

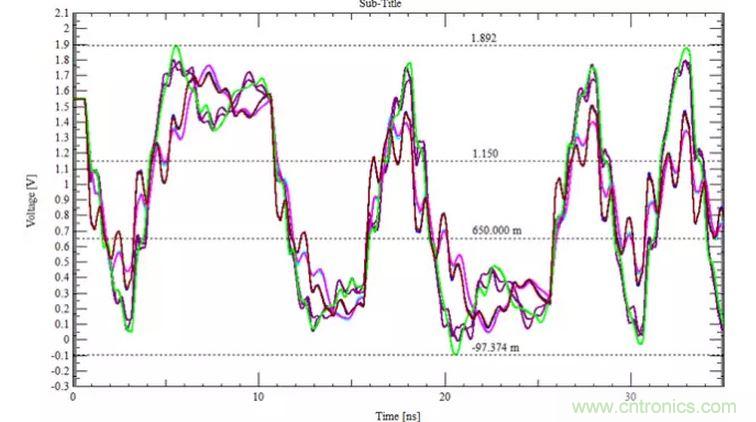

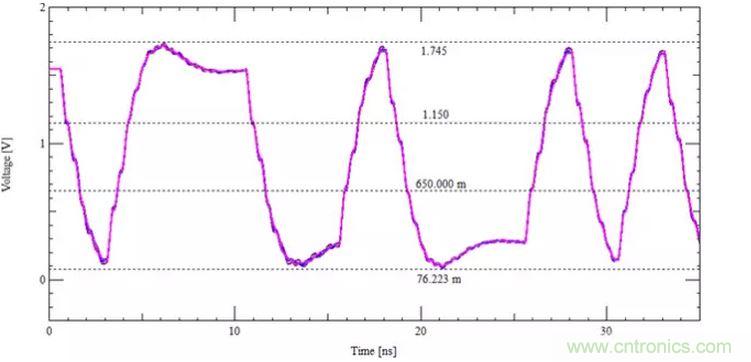

地址信號一拖八也采用T型結構,按照上面對T型結構的說明,主干要長分支盡量短且對稱的原則,我們可以看到這個地址信號的走線結構就比較凌亂,可想而知信號肯定會很差。且看原始設計和改善后的仿真結果對比。

原始版本的地址信號仿真結果

[page]

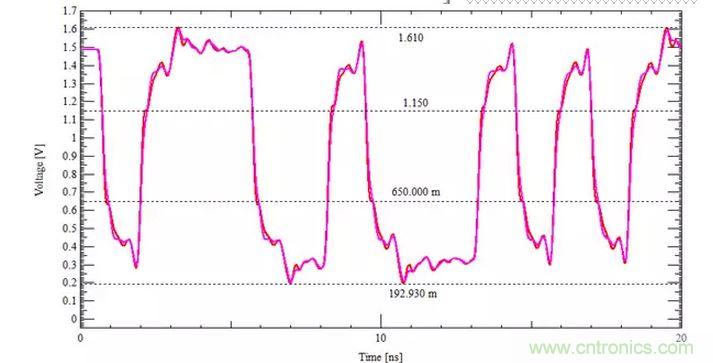

改善后的地址信號仿真結果

DQS信號也大致一樣,沒有按照T型結構的最好原則來布線,不再贅述。最后來看數(shù)據(jù)信號,數(shù)據(jù)信號需要完全參照DQS信號走線,包括等長。好了,現(xiàn)在的數(shù)據(jù)信號卻走成了菊花鏈結構,且沒法和DQS去做嚴格的等長,另外信號之間的間距也很小,容易引起串擾問題,真的很任性!

原始版本的數(shù)據(jù)信號寫操作仿真結果

改善后的數(shù)據(jù)信號寫操作仿真結果

上面只是每組信號的單獨分析,再看看全局的一些考慮吧。

1、總體上加了太多的串阻,占用了布線空間且多打出許多過孔。

2、地址、命令和控制信號需要和對應的時鐘信號保持一定的等長(等長范圍視具體芯片來定,一般在±200mil)。

3、數(shù)據(jù)組需要和對應的DQS信號等長(一般在50mil內),盡量同組信號同層布線。

4、數(shù)據(jù)組與對應的時鐘信號也需要有一定的等長,為了給后續(xù)調試留出更多的裕量,一般這個等長比時序仿真出來的結果更短,常見的在±500mil內。因為參考的時鐘關系,這也意味著數(shù)據(jù)組與組之間的長度偏差也在±500mil內。當然這些等長范圍都是一些經驗值,具體的更要看對應的芯片。

好了,以上只是對DDR2的設計做了一部分常規(guī)性的總結,那么問題來了~