【導(dǎo)讀】按照許多年前老師的教導(dǎo),我們會(huì)在運(yùn)算放大器的兩個(gè)輸入端放上相等的阻抗。本文探究為什么會(huì)有這么一條經(jīng)驗(yàn)法則����,以及我們是否應(yīng)當(dāng)遵循這種做法���。

如果您是在741運(yùn)算放大器1橫行天下的時(shí)代長(zhǎng)大的�,那么平衡運(yùn)算放大器輸入端電阻的觀念必定已扎根在您的頭腦中。隨著時(shí)間的流逝��,由于不同電路技術(shù)和不同IC工藝的出現(xiàn)�,這樣做可能不再是對(duì)的。事實(shí)上�����,它可能引起更大直流誤差和更多噪聲�,使電路更不穩(wěn)定。我們以前為什么要那樣做����?什么變化導(dǎo)致我們現(xiàn)在這樣做可能是錯(cuò)誤的?

在二十世紀(jì)六十年代和七十年代���,第一代運(yùn)算放大器采用普通雙極性工藝制造�����。為獲得合理的速度���,差分對(duì)電流源電流一般在10 μA到20 μA范圍內(nèi)。

而β值為40到70���,故輸入偏置電流在1 μA左右�����。然而�����,晶體管匹配度不是那么高�����,所以輸入偏置電流不相等����,導(dǎo)致輸入偏置電流之間有10%到20%的偏差(稱為"輸入失調(diào)電流")����。

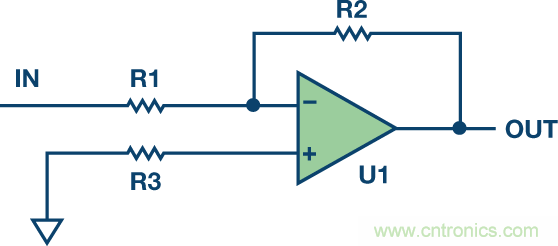

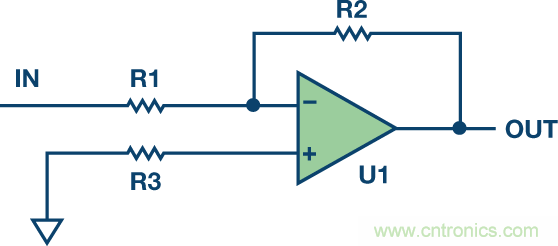

在同相接地輸入端增加一個(gè)與輸入電阻R1和反饋電阻R2的并聯(lián)組合相等的電阻(圖1中的R3),可以讓阻抗相等�。做一些計(jì)算可以證明,誤差降至Ioffset × R feedback �����。由于I offset 為I bias 的10%到20%,所以這會(huì)有助于降低輸出失調(diào)誤差�����。

圖1. 經(jīng)典反相放大器

直流誤差

為降低雙極性運(yùn)算放大器的輸入偏置電流�����,許多運(yùn)算放大器設(shè)計(jì)集成了輸入偏置電流消除功能�。OP07就是一個(gè)例子。輸入偏置電流消除功能的增加使偏置電流大大降低�����,但輸入失調(diào)電流可能為剩余偏置電流的50%到100%�����,所以增加電阻的作用非常有限����。某些情況下,增加電阻反而可能導(dǎo)致輸出誤差提高�。 噪聲

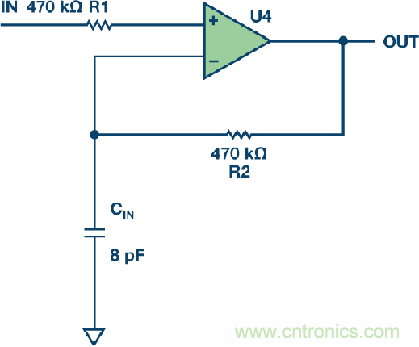

電阻熱噪聲的計(jì)算公式為√4kTRB,故1 kΩ電阻會(huì)有4 nV/√Hz的噪聲���。增加電阻會(huì)增加噪聲�����。在圖2中�,出人意料的是�,雖然909 Ω補(bǔ)償電阻是值最低的電阻,但由于從該節(jié)點(diǎn)到輸出端的噪聲增益�����,它給圖2輸出端貢獻(xiàn)的噪聲最多�����。R1引起的輸出噪聲為40 nV/√Hz�����,R2為12.6 nV/√Hz���,R3為42 nV/√Hz���。因此�,請(qǐng)勿使用電阻���。另一方面�����,如果運(yùn)算放大器采用雙電源供電�,并且一個(gè)電源先于另一個(gè)電源上電����,那么ESD網(wǎng)絡(luò)可能發(fā)生閂鎖問(wèn)題。這種情況下�,可能希望增加一定的電阻來(lái)保護(hù)器件。但若使用的話���,應(yīng)在電阻上放置一個(gè)旁路電容以減少電阻的噪聲貢獻(xiàn)����。

圖2. 噪聲分析

穩(wěn)定性

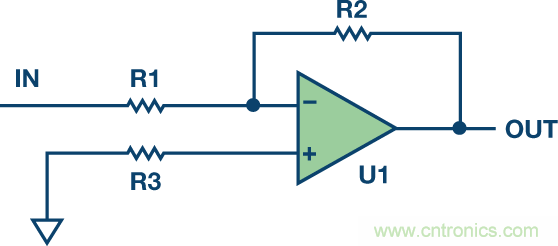

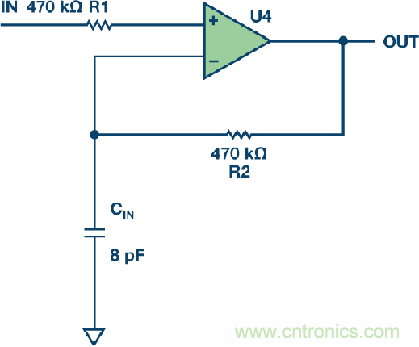

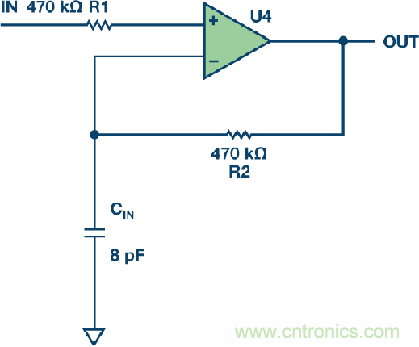

所有運(yùn)算放大器都有一定的輸入電容����,包括差分和共模。如果運(yùn)算放大器連接為跟隨器��,并且在反饋路徑中放入一個(gè)電阻以平衡阻抗,那么系統(tǒng)可能容易發(fā)生振蕩��。原因是:大反饋電阻���、運(yùn)算放大器的輸入電容和PC板上的雜散電容會(huì)形成一個(gè)RC低通濾波器(LPF)����。此濾波器會(huì)引起相移����,并降低閉環(huán)系統(tǒng)的相位裕量��。如果降低得太多����,運(yùn)算放大器就會(huì)振蕩。一位客戶在一個(gè)1 Hz Sallen-Key低通濾波器電路中使用AD8628 CMOS運(yùn)算放大器�����。由于轉(zhuǎn)折頻率較低�����,電阻和電容相當(dāng)大(參見(jiàn)圖3)。輸入電阻為470 kΩ�,所以客戶在反饋路徑中放入一個(gè)470 kΩ電阻。此電阻與8 pF的輸入電容(參見(jiàn)圖4)一起提供一個(gè)42 kHz極點(diǎn)����。AD8628的增益帶寬積為2 MHz,因此它在42 kHz仍有大量增益�����,它發(fā)生了軌到軌振蕩�����。把470 kΩ電阻換成0 Ω跳線即解決了問(wèn)題��。因此�,反饋路徑中應(yīng)避免使用大電阻。這里��,何者為大取決于運(yùn)算放大器的增益帶寬����。對(duì)于高頻運(yùn)算放大器,例如增益帶寬超過(guò)400 MHz的ADA4817-1,1 kΩ反饋電阻就稱得上是大電阻�。務(wù)必閱讀數(shù)據(jù)手冊(cè)以了解其中的建議。

圖3. 您所見(jiàn)

圖4. 電子所見(jiàn)

結(jié)語(yǔ)

多年來(lái)的實(shí)踐會(huì)產(chǎn)生一些有用的經(jīng)驗(yàn)法則�����。審核設(shè)計(jì)時(shí)����,仔細(xì)檢視這些規(guī)則,判定它們是否仍然適用是很好的做法����。關(guān)于是否需要增加平衡電阻��,如果運(yùn)算放大器是帶有輸入偏置電流消除功能的CMOS��、JFET或雙極型�,那么很可能不需要添加。