【導(dǎo)讀】模數(shù)轉(zhuǎn)換器(ADC)很久以來一直是通信接收機設(shè)計的基本器件。隨著通信技術(shù)的不斷發(fā)展,消費者要求更快的數(shù)據(jù)速率和更低的服務(wù)價格。提供這項技術(shù)的回程服務(wù)供應(yīng)商面臨著兩難的處境。更高的數(shù)據(jù)速率意味著更多帶寬,這也就表示更快的數(shù)據(jù)轉(zhuǎn)換器,將模擬無線電波轉(zhuǎn)換為數(shù)字處理。然而,更快的數(shù)據(jù)轉(zhuǎn)換器(GSPS,或稱每秒千兆采樣轉(zhuǎn)換器)——廣為人知的有RF采樣ADC——同樣產(chǎn)生大量數(shù)據(jù),而這些DSP芯片必須以高得多的速度進行處理。這無疑增加了無線電接收機的運營成本。

解決方案是對組成RF采樣ADC的硅芯片進行更優(yōu)化設(shè)計。得益于硅芯片工藝的進步(感謝摩爾定律),定制型數(shù)字處理模塊中的RF采樣ADC在功耗和尺寸方面的效率相比現(xiàn)有FPGA要更高。使用這些數(shù)字信號處理模塊還能獲得更低的數(shù)據(jù)速率,從而可以使用成本更低的FPGA。這對于運營商來說是雙贏的局面,因為他們可以使用這些GSPS ADC以高頻率進行采樣、使用內(nèi)部數(shù)字下變頻器(DDC)以所需速度處理數(shù)據(jù),并以能實現(xiàn)的(低)數(shù)據(jù)速率將其發(fā)送至更為廉價的FPGA(或者現(xiàn)有的ASIC產(chǎn)品)進行進一步的基帶處理。

使用帶有DDC的RF采樣ADC的另一個優(yōu)勢是,這樣可以通過更靈活、更緊湊、性價比更高的方式實現(xiàn)雙頻段無線電系統(tǒng)。雙頻段無線電系統(tǒng)的應(yīng)用已有多年歷史。基站系統(tǒng)設(shè)計人員以前通過使用兩個獨立的無線電路徑(每頻段一個)來實現(xiàn)雙頻段無線電系統(tǒng)。本文討論一種利用多頻段無線電接收機——使用RF采樣ADC,比 如AD9680——對兩個獨立而使用廣泛的頻段進行數(shù)字化和處理。本文第一部分解釋了功能框圖級別的實現(xiàn),并討論了雙頻段無線電系統(tǒng)中使用GSPS ADC的優(yōu)勢。本文第二部分將討論TDD LTE頻段34和39(亦分別稱為頻段A和頻段F)的實現(xiàn)和數(shù)據(jù)分析,并通過數(shù)據(jù)分析來揭示顯示器性能。

傳統(tǒng)雙頻段無線電接收機

為了迎合客戶對于雙頻段無線電的需求,同時滿足總系統(tǒng)級性能要求,基站設(shè)計人員拿出了他們的看家本領(lǐng):復(fù)制兩次無線電設(shè)計,然后每頻段調(diào)諧一個設(shè)計。這意味著針對客戶的選擇,設(shè)計人員必須將兩個獨立的無線電硬件設(shè)計調(diào)諧至兩個頻段。

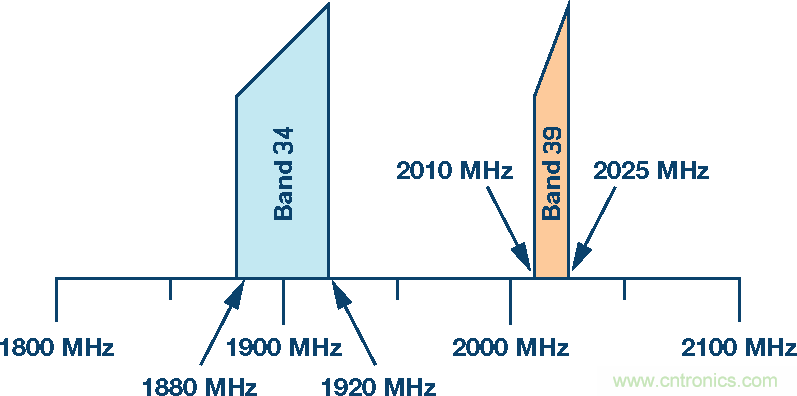

例如,如果需要構(gòu)建能支持TDD LTE頻段34(頻段A:2010 MHz至2025 MHz)以及頻段39(頻段F:1880 MHz至1920 MHz)1的無線電接收機,則設(shè)計人員就會打包兩個無線電接收機設(shè)計。TDD LTE頻段的頻率規(guī)劃如圖1所示。

圖1. TDD LTE頻段34和39的頻率規(guī)劃。

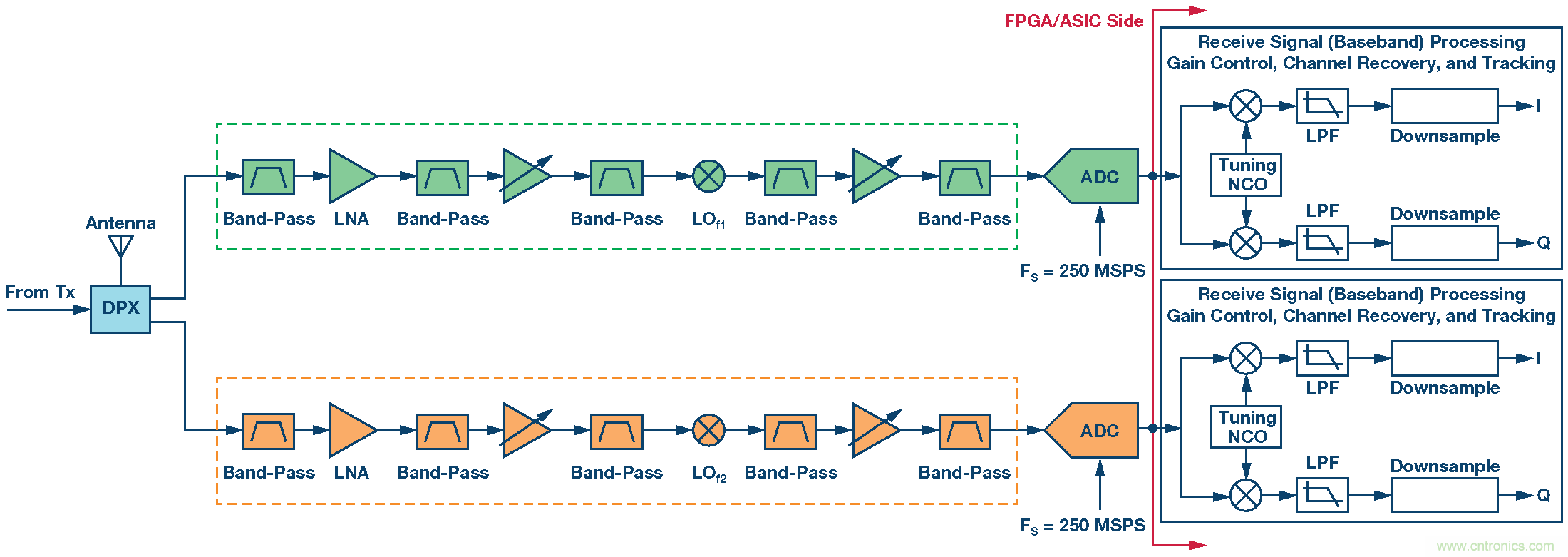

設(shè)計雙頻段無線電接收機以支持這些頻段的傳統(tǒng)方法是部署兩個獨立的接收機鏈路,每頻段一個。下文圖2顯示了雙頻段無線電接收機的框圖。2

圖2. 雙頻段無線電接收機設(shè)計的傳統(tǒng)方法。

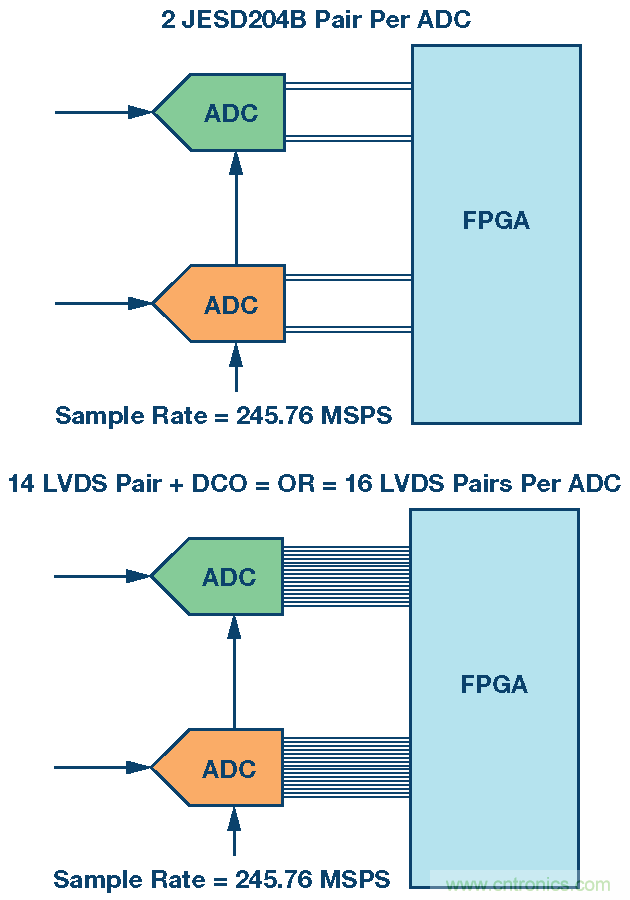

圖2顯示了雙頻段無線電的傳統(tǒng)實現(xiàn)。該方案的實現(xiàn)成本較高,因為它實際上是一個系統(tǒng)中的兩個無線電接收機。每一個處理元件都是重復(fù)的,以便支持對應(yīng)頻段。FPGA資源也是如此。每一個處理元件都是重復(fù)的,以便支持對應(yīng)頻段,這導(dǎo)致FPGA資源重復(fù),增加系統(tǒng)成本和復(fù)雜性,導(dǎo)致功耗上升。就FPGA接口來說,F(xiàn)PGA資源也將是兩倍,以支持兩個ADC數(shù)據(jù)流。圖3顯示了FPGA I/O資源要求或雙頻段無線電接收機系統(tǒng)設(shè)計的框圖。該圖同時顯示了LVDS和JESD204B ADC接口。LVDS數(shù)據(jù)速率較低,但FPGA需要更高的I/O數(shù)。JESD204B接口需要較少的FPGA I/O資源,但通道速率可能更高,因此FPGA也許更為昂貴。

圖3. 傳統(tǒng)雙頻段無線電接收機的FPGA接口要求。

使用RF采樣(GSPS) ADC的雙頻段無線電接收機

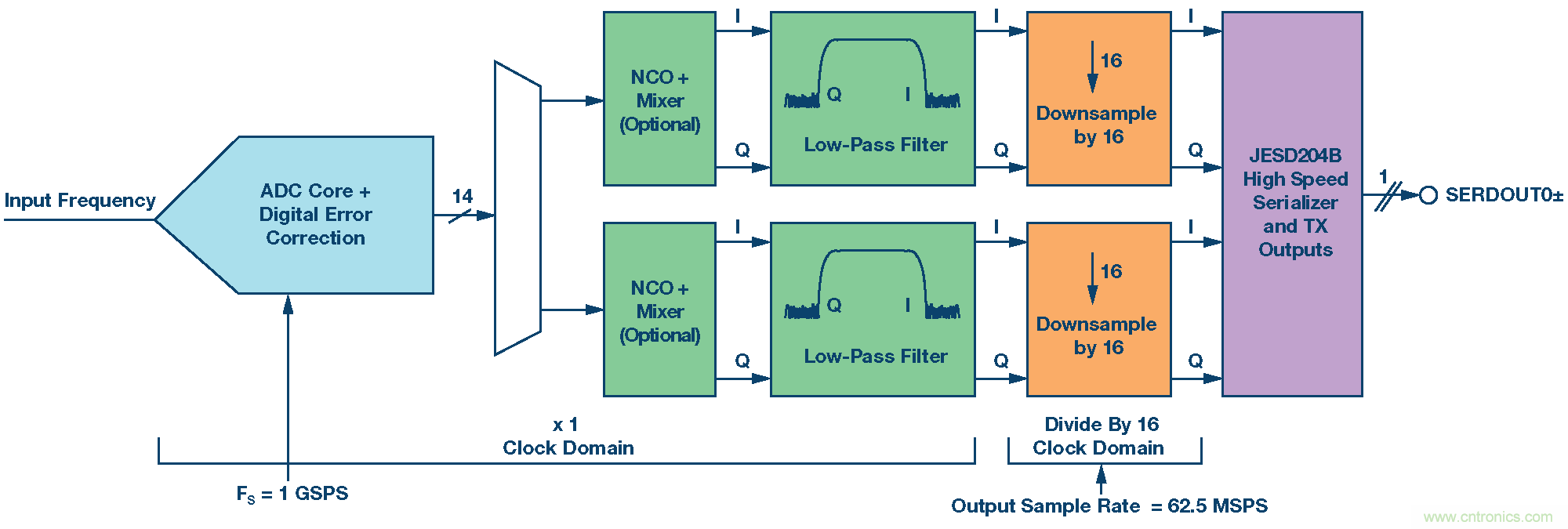

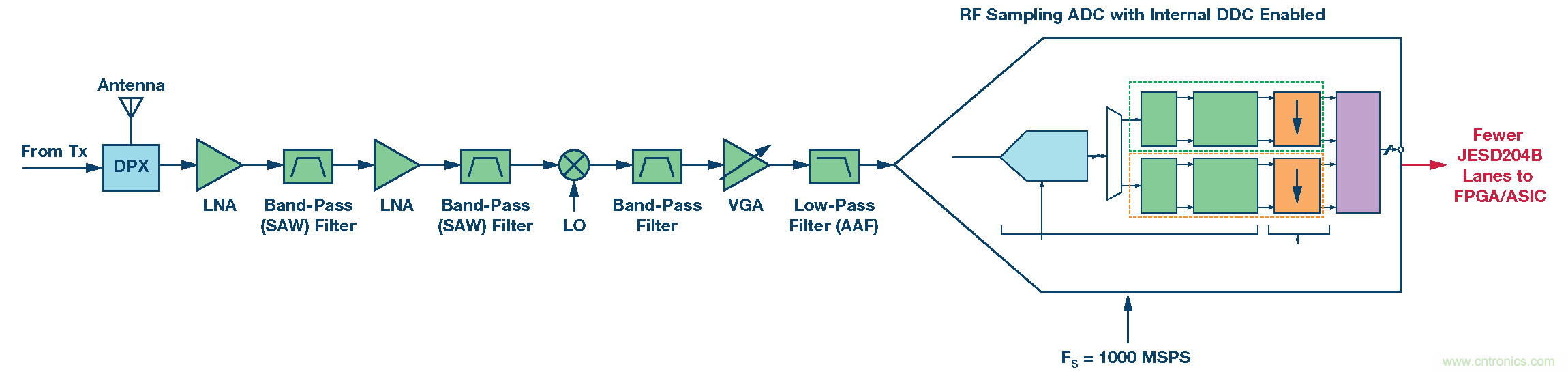

RF采樣或GSPS ADC能夠提供系統(tǒng)設(shè)計靈活性。利用深亞微米工藝技術(shù),GSPS ADC可以集成數(shù)字處理模塊,且相比FPGA以低得多的功耗進行特定速度下的數(shù)據(jù)操作。RF采樣ADC的核心是一個高帶寬模擬采樣內(nèi)核,以GHz速度進行采樣。模擬內(nèi)核之后是各種各樣的數(shù)字信號處理元件。這些數(shù)字下變頻器可以用來提取相應(yīng)頻段。針對雙頻段接收機設(shè)置的RF采樣ADC內(nèi)部框圖如圖4所示。DDC除了處理信號,還可降低JESD204B通道數(shù)據(jù)的通道速率。

圖4. 顯示內(nèi)部DDC的RF采樣ADC框圖。

加入數(shù)字信號處理模塊后,GSPS ADC便可以獨立方便地提供兩個處理頻段。這對于運營商來說是雙贏的局面,因為他們可以使用這些RF采樣ADC以高頻率進行采樣、使用內(nèi)部數(shù)字下變頻器(DDC)以所需速度處理數(shù)據(jù),并以能實現(xiàn)的(低)數(shù)據(jù)速率將其發(fā)送至更為廉價的FPGA(或者現(xiàn)有的ASIC產(chǎn)品)進行進一步的基帶處理。這些ADC提供高帶寬前端,讓系統(tǒng)設(shè)計人員能夠捕捉寬頻率范圍(比如兩個無線電頻段)并對其數(shù)字化,以便進行信號處理。下文圖5顯示了一個雙頻段接收機系統(tǒng),使用RF采樣ADC和內(nèi)部DDC來提取頻段。顯然,與圖2中的方案進行對照后發(fā)現(xiàn),使用RF采樣ADC的雙頻段接收機在實現(xiàn)上要簡單得多。在本方案中,RF向下混頻至高中頻,其寬度為幾百MHz,而不是傳統(tǒng)雙頻段應(yīng)用的幾十MHz寬度。BPF和VGA級為可選,取決于所需的系統(tǒng)性能等級。

圖5. 使用RF采樣ADC和內(nèi)部DDC來提取頻段的雙頻段無線電接收機。

在雙頻段無線電系統(tǒng)中使用RF采樣ADC的部分優(yōu)勢如下所述:

更簡單的前端設(shè)計

使用RF采樣ADC的雙頻段無線電系統(tǒng)設(shè)計大幅簡化了前端網(wǎng)絡(luò)。對于剛接觸的用戶來說,只需進行一次前端設(shè)計,而不是兩次(每頻段一次)。這樣可以大幅降低系統(tǒng)板的物料清單。接下來是AAF(抗混疊濾波器)要求,它是用于兩個中頻轉(zhuǎn)換器的帶通濾波器(BPF)——相比用于GSPS ADC的低通濾波器(LPF)而言。這是因為GSPS ADC對輸入信號進行過采樣。3, 4數(shù)據(jù)過采樣后,數(shù)字下變頻器就能進行抽取和濾波。如果頻率規(guī)劃使二次和三次諧波落在頻段外,那么就可放寬AAF要求。

更低的系統(tǒng)功耗,更小的尺寸

RF采樣只需一個前端(如圖5所示),而不是兩個LNA、兩個混頻器和兩個IF ADC(如圖2所示)。從系統(tǒng)級功耗角度來看,這樣可以大幅降低功耗。較低的系統(tǒng)功耗以及更簡單的前端設(shè)計縮小了系統(tǒng)的尺寸。

更高的FPGA利用率

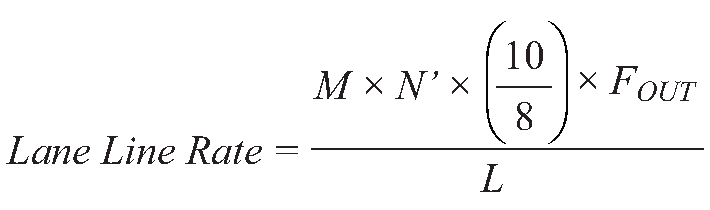

使用RF采樣ADC來實現(xiàn)雙頻段無線電系統(tǒng)時,通過DDC來提取各頻段。由于DDC抽取數(shù)據(jù),因而降低了輸出采樣速率。這使JESD204B接口的配置非常靈活。例如,某個雙通道ADC以1GSPS速率采樣,并且工作在全帶寬模式,則四個通道的線路速率計算值為每通道10Gbps。ADI公司的JESD204B轉(zhuǎn)換器線路速率可以計算如下:

其中

M = 轉(zhuǎn)換器數(shù)(本例中為2)

N'''' = 每個樣本的轉(zhuǎn)換器位數(shù)(本例中為16)

10/8 = 8B10B 開銷

FOUT = 輸出采樣速率; 本例中, Decimation_Ratio = 1 針對全帶寬)

L = 通道數(shù)(本例中為4)

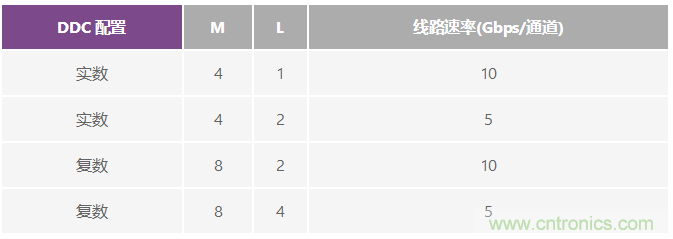

舉例而言,如果同樣的雙通道ADC使用總共4個DDC的8抽取配置,則ADC可支持很多配置,具體取決于通道數(shù)。輸出采樣速率變?yōu)?25 MSPS (1 GSPS ÷ 8)。各種配置如表1所示:

表1

這些靈活的配置為系統(tǒng)設(shè)計人員提供了以下選擇自由:使用具有較高通道速率但更佳I/O通道密度使用率的昂貴FPGA,或者使用存在線路速率限制的現(xiàn)有FPGA/ASIC。

結(jié)論

GSPS ADC深亞微米硅工藝的出現(xiàn)迎來了無線電架構(gòu)討論與設(shè)計的新紀(jì)元。GSPS ADC具有高帶寬采樣內(nèi)核以及數(shù)字下變頻器選項,提供重新思考和重新定義無線電架構(gòu)的靈活思路,從而滿足消費者不斷增長的需要。這些GSPS ADC具有更低的功耗和更小的尺寸,可降低這些無線電產(chǎn)品的擁有成本。集成JESD204B接口的當(dāng)代ADC具有靈活的輸出選項,它們并不妨礙系統(tǒng)設(shè)計人員使用昂貴的高線路速率FPGA或數(shù)字邏輯。

本文第二部分將討論TDD LTE頻段34和39相關(guān)的使用場景,并分析它在采用AD9680的多頻段無線電接收機中的應(yīng)用。5

參考電路

1 E-UTRA頻段.

2 Walt Kester. 數(shù)據(jù)轉(zhuǎn)換手冊 。ADI公司,2005年。

3 Umesh Jayamohan. "祖父時代的ADC已成往事:RF采樣ADC給系統(tǒng)設(shè)計帶來諸多好處。"ADI公司,2015年。

4 過采樣。.

5 AD9680. ADI 公司。

推薦閱讀: