【導讀】當前許多精密模數(shù)轉換器(ADC)具有串行外設接口(SPI)或某種串行接口,用以與包括微控制器單元(MCU)、DSP和FPGA在內的控制器進行通信??刂破鲗懭牖蜃x取ADC內部寄存器并讀取轉換碼。SPI的印刷電路板(PCB)布線簡單,并且有比并行接口更快的時鐘速率,因而越來越受歡迎。而且,使用標準SPI很容易將ADC連接到控制器。

一些新型ADC具有SPI,但有些ADC具有非標準的3線或4線SPI作為從機,因為它們希望實現(xiàn)更快的吞吐速率。例如,AD7616, AD7606 和 AD7606B系列有兩條或四條SDO線,在串行模式下可提供更快的吞吐速率。AD7768, AD7779和AD7134系列有多條SDO線,用作SPI主機。用戶在設計微控制器SPI以配置ADC和讀取代碼時往往會遇到困難。

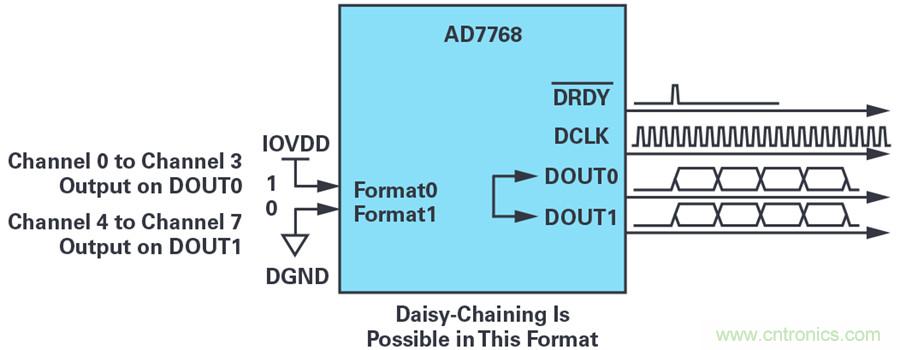

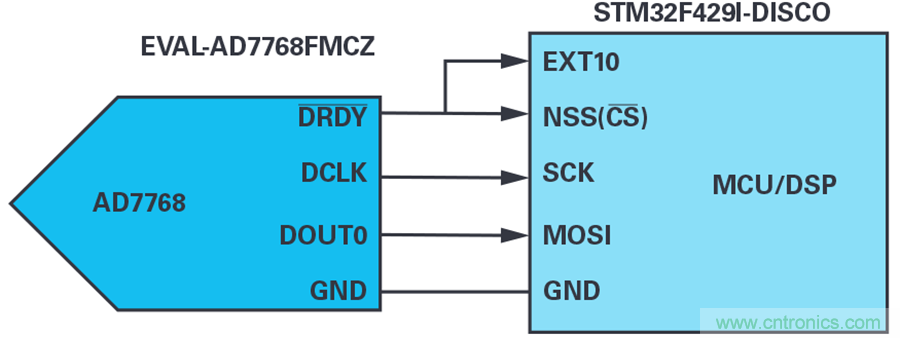

圖1. AD7768用作串行主機,具有兩個數(shù)據(jù)輸出引腳(14001-193)。

與ADC的標準MCU SPI連接

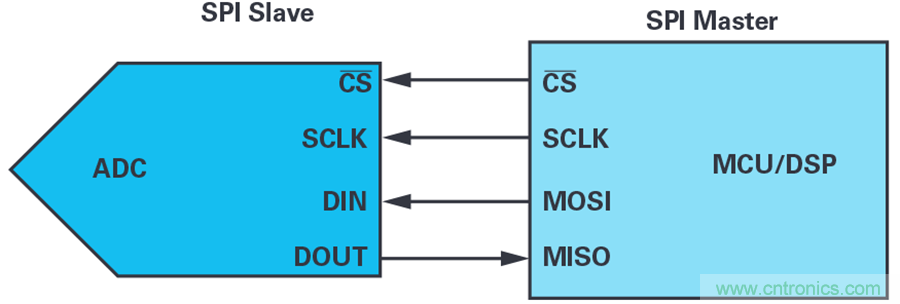

SPI是一種同步、全雙工、主從式接口。來自主機或從機的數(shù)據(jù)在時鐘上升沿或下降沿同步。主機和從機可以同時傳輸數(shù)據(jù)。圖2顯示了典型的4線MCU SPI接口連接。

圖2. 與ADC從機的標準MCU SPI連接。

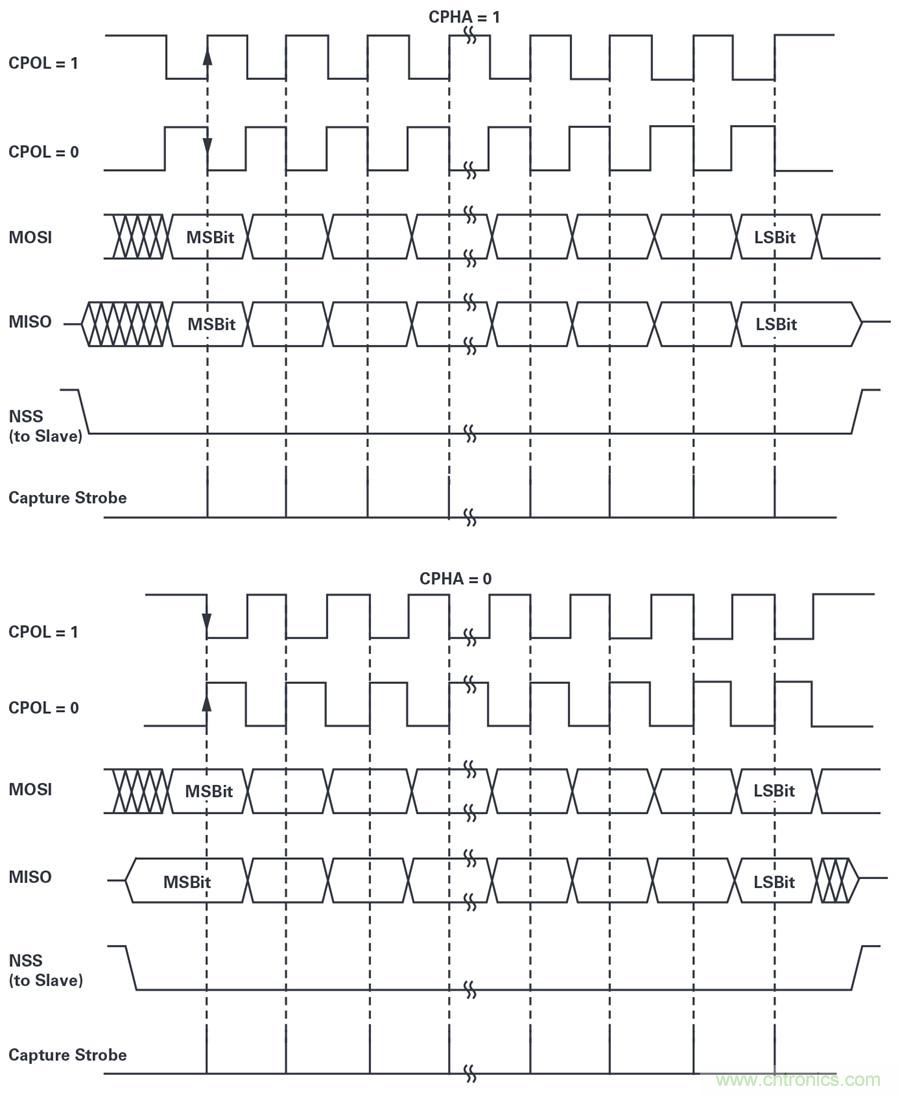

要開始SPI通信,控制器必須發(fā)送時鐘信號,并通過使能 CS 信號(通常是低電平有效信號)來選擇ADC。SPI是全雙工接口,因此控制器和ADC可以分別通過MOSI/DIN和MISO/DOUT線同時輸出數(shù)據(jù)??刂破鱏PI接口允許用戶靈活選擇時鐘的上升沿或下降沿來采樣和/或移位數(shù)據(jù)。為了在主機和從機之間進行可靠的通信,用戶必須遵守微控制器和ADC芯片的數(shù)字接口時序規(guī)范。

圖3. SPI數(shù)據(jù)時鐘時序圖示例。

如果微控制器SPI和ADC串行接口具有標準SPI時序模式,那么用戶設計PCB布線和開發(fā)驅動器固件不成問題。

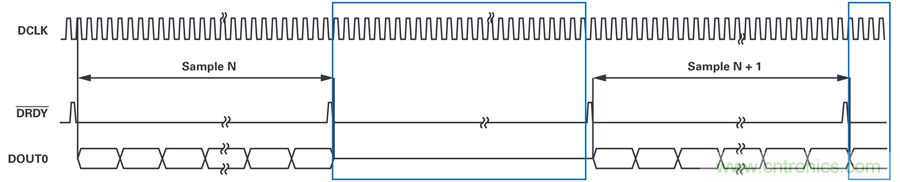

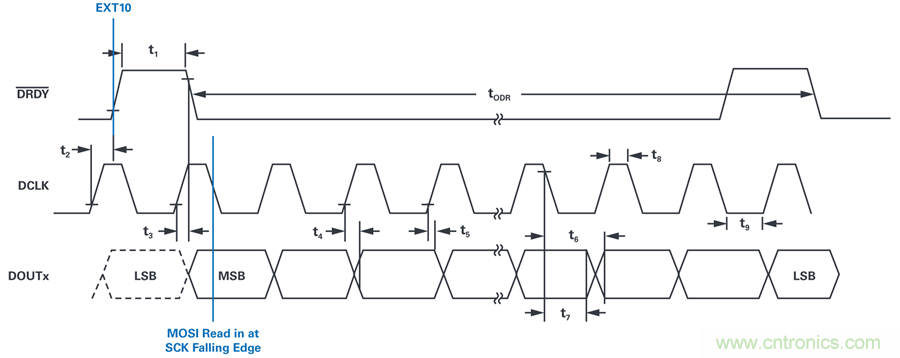

但是,有些新型ADC的串行接口端口不是典型的SPI時序模式。MCU或DSP似乎不可能通過AD7768串行端口(一種非標準時序SPI端口)讀取數(shù)據(jù),如圖4所示。

圖4. AD7768 FORMATx = 1×時序圖,僅通過DOUT0輸出。

與STM32F429 SPI連接

如何操縱標準微控制器SPI以便與具有非標準SPI端口的ADC接口讀取數(shù)據(jù)呢?以STM32F429微控制器讀取AD7768數(shù)據(jù)為例。如圖4所示,當FORMATx = 11或10時,通道0至通道7僅通過DOUT0輸出 數(shù)據(jù)。在標準工作模式下, AD7768/AD7768-4 作為主機工作,數(shù)據(jù)流入MCU、DSP或FPGA。AD7768/AD7768-4向從機提供數(shù)據(jù)、數(shù)據(jù)時鐘(DCLK)和下降沿幀使能信號(DRDY)。

STM32Fxxx系列微控制器廣泛用于很多不同的應用中。該MCU有多個SPI端口,可以使用典型的SPI時序模式將其配置為SPI主機或從機。

AD7768/AD7768-4分別為8通道和4通道同步采樣∑-?型ADC,每通道均有∑-?型調制器和數(shù)字濾波器,支持交流和直流信號的同步采樣。這些器件在110.8 kHz的最大輸入帶寬下實現(xiàn)了108 dB動態(tài)范圍,具備±2 ppm INL、±50 µV偏置誤差和±30 ppm增益誤差的典型性能。AD7768/AD7768-4用戶可在輸入帶寬、輸出數(shù)據(jù)速率和功耗之間進行權衡,并選擇三種功耗模式之一以優(yōu)化噪聲目標和功耗。AD7768/AD7768-4的靈活性使其成為適合低功耗直流和高性能交流測量模塊的可重復使用平臺。

遺憾的是,AD7768的串行接口不是典型SPI時序模式,而且AD7768充當串行接口主機。一般而言,用戶必須使用FPGA/CPLD作為其控制器,例如,使用32F429IDISCOVERY和AD7768評估板。變通SPI線的連接如圖5所示。在這種設置下,AD7768的所有八通道數(shù)據(jù)僅通過DOUT0輸出。

圖5. AD7768通過DOUT0將數(shù)據(jù)輸出到STM32F429 MCU SPI連接。

需要解決的問題:

● AD7768用作SPI主機,故必須將STM32F429I SPI配置為SPI從機。

● DRDY 高電平脈沖只持續(xù)一個DCLK周期,這不是典型的CS。

● 完成所有通道數(shù)據(jù)位的輸出之后,DCLK繼續(xù)輸出,DRDY為低電平。

圖6. 時序解決方案中的AD7768數(shù)據(jù)位讀取。

解決方案:MCU SPI作為從機,通過一條DOUT線與SPI主機ADC接口。

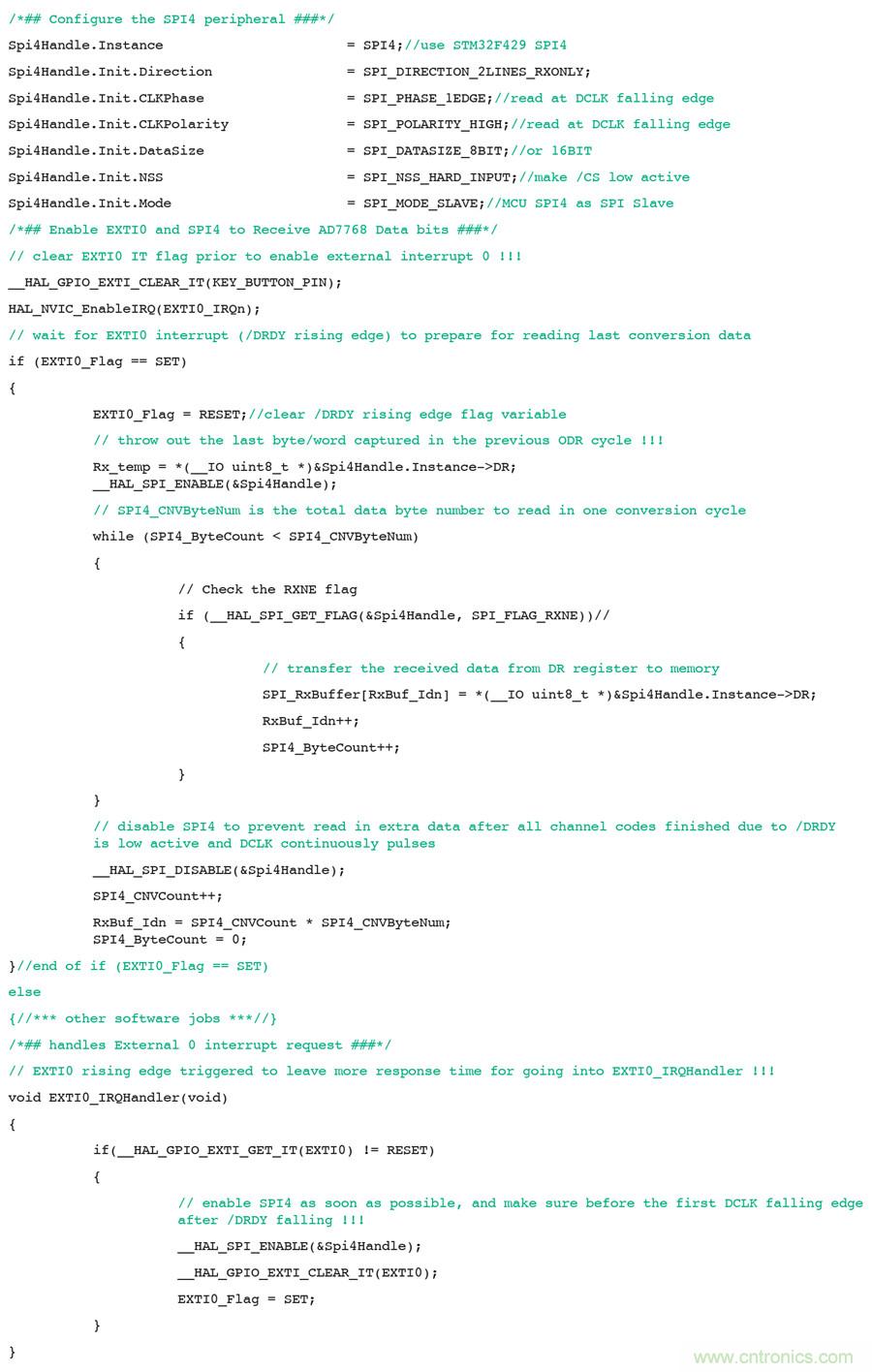

● 將STM32F429的一個SPI端口(如SPI4)配置為從機,以DCLK速率接收MOSI上的數(shù)據(jù)位。

● 將AD7768DRDY 連接到STM32F429外部中斷輸入引腳EXTI0和NSS (SPI CS) 引腳。 DRDY 的上升沿將觸發(fā)EXTI0處理例程,以使SPI從機能夠在DRDY 變?yōu)榈碗娖街蟮牡谝粋€DCLK下降沿開始接收數(shù)據(jù)位。時序設計在這里至關重要。

● 接收到通道0至通道7的所有數(shù)據(jù)后,應禁用SPI以防止讀取額外的無效數(shù)據(jù),因為 DRDY 會使SPI從機 CS 變?yōu)榈碗娖?,并且DCLK保持切換。

MCU固件開發(fā)注意事項

圖7. 配SPI4外設。

當軟件處于中斷模式時,DCLK運行速率可以高達4 MHz,實現(xiàn)8 kSPS的 ODR。軟件應進入中斷處理程序,在一個半DCLK周期(375 ns)內啟動SPI。為使軟件更輕松地進入中斷例程,MCU可以在DCLK上升沿讀取數(shù)據(jù),從而提供額外的半個DCLK周期時間。但是, t5 DCLK上升到DOUTx無效最小值為–3 ns(IOVDD = 1.8 V時為–4 ns),因此DOUTx上的傳播延遲(>|t5| + MCU 保持時間) 應通過PCB布線或緩沖增加。

推薦閱讀: