【導(dǎo)讀】在許多控制系統(tǒng)的核心區(qū)域,數(shù)模轉(zhuǎn)換器 (DAC) 在決定系統(tǒng)的性能和精度方面起著非常關(guān)鍵的作用。本文將介紹兩款新的精密 16 位 DAC,并對通過緩沖高速互補電流輸出 DAC 的輸出以實現(xiàn)變壓器同等性能的創(chuàng)意進行討論。

片內(nèi)系統(tǒng)基準(zhǔn)電壓源改善了精度

在惡劣環(huán)境下運行的電子系統(tǒng)可能必須在忍受極端溫度的同時保持出色的精度和穩(wěn)定性。此類系統(tǒng)往往需要多個分辨率高達(dá) 16 位的數(shù)模擬轉(zhuǎn)換器。DAC 輸出電壓的精度最終取決于其基準(zhǔn)電壓的精度。為了在各種溫度下實現(xiàn)這種水平的性能,通常會使用單獨的精密基準(zhǔn)電壓源。然而,現(xiàn)在推出了包含低漂移基準(zhǔn)電壓源的全新精密四通道 DAC 系列,它的性能足夠好,可以作為系統(tǒng)基準(zhǔn)電壓源。

基準(zhǔn)電壓源應(yīng)在各種不同的負(fù)載、電源變化和溫度條件下保持恒定的電壓。不幸的是,高性能的獨立基準(zhǔn)電壓源往往體積較大、成本昂貴且功耗高 — 而片內(nèi)基準(zhǔn)電壓源往往性能不佳。

直到現(xiàn)在,當(dāng)系統(tǒng)設(shè)計師面臨是將精密的 DAC 與外部基準(zhǔn)電壓源配對,還是承受低性能片內(nèi)基準(zhǔn)電壓源帶來的痛苦時,往往不得不選擇 DAC 和外部基準(zhǔn)電壓源。他們不能指望片內(nèi)基準(zhǔn)電壓源的性能,因為這些電壓源在各種溫度下變化極大,而且往往缺少最大 TC 規(guī)格,無法用作系統(tǒng)基準(zhǔn)電壓源。

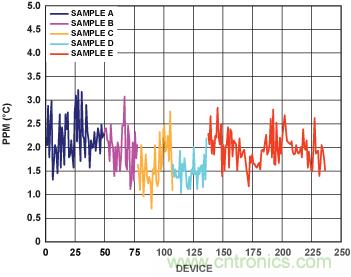

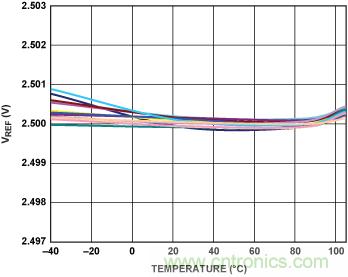

AD5686R 打破了這一慣例。這款四通道、電壓輸出、16 位 nanoDAC+® 數(shù)模轉(zhuǎn)換器提供了 2.5 V 片內(nèi)基準(zhǔn)電壓源,并且最大溫度漂移為 5 ppm/°C(通常為 2 ppm/°C)。這一性能水平與獨立基準(zhǔn)電壓源的性能水平相當(dāng),使得片內(nèi)基準(zhǔn)電壓源可以取代系統(tǒng)基準(zhǔn)電壓源,從而節(jié)省空間、成本和功耗。5-ppm/°C 的最大漂移規(guī)格允許進行精密誤差量計算。圖 1 和圖 2 顯示了 AD5686R’ 片內(nèi)基準(zhǔn)電壓源的性能。圖 1 顯示了五個單獨采樣批次的數(shù)百個 DAC 的溫度系數(shù)散布圖。圖 2 顯示了九個 DAC 在 –40°C 至 +105°C 溫度范圍內(nèi)的實際輸出電壓。

圖 1. 數(shù)百個 AD5686R DAC 的溫度系數(shù)。

圖 2. 九個典型 AD5686R DAC 的基準(zhǔn)電壓和溫度。

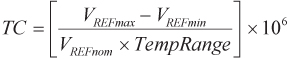

方法:對于參考電壓,溫度系數(shù) (TC) 通常使用箱式方法確定,該方法在規(guī)定的溫度范圍內(nèi)評估最大電壓變化。TC 以 ppm/°C 為單位,按照以下方程式計算

其中

VREFmax 是在溫度范圍內(nèi)測得的最大基準(zhǔn)電壓輸出。

VREFmin 是在溫度范圍內(nèi)測得的最小基準(zhǔn)電壓輸出。

VREFnom 是標(biāo)稱基準(zhǔn)輸出電壓。

TempRange 是規(guī)定的溫度范圍 (°C)。

低溫系數(shù)是通過加熱生產(chǎn)中零件并微調(diào)輸出電壓以補償隨溫度變化的曲線而得出的。緊密配合可以確保電阻差異不會影響基準(zhǔn)電壓源的性能,并且還讓 DAC 達(dá)到極其出色的 ±2-LSB 積分非線性 (INL) 規(guī)格。

關(guān)于 AD5686R/AD5685R/AD5684R

AD5686R/AD5685R/AD5684R 屬于 nanoDAC+ 系列,它們是四通道、低功耗、16/14/12 位 DAC,提供經(jīng)過緩沖的電壓輸出。市場對精度高、操作簡便且封裝尺寸小巧的數(shù)模轉(zhuǎn)換器的需求日益增多,nanoDAC+ 系列正是為了滿足這一需求而開發(fā)的。這些新器件包含已默認(rèn)啟用的片內(nèi) 2.5V 2-ppm/°C 基準(zhǔn)電壓源。增益選擇引腳可將滿度輸出設(shè)置為 2.5 V (GAIN = 1) 或 5 V (GAIN = 2)。這些器件采用單個 2.7 V 至 5.5 V 電源,具有 0.1% 的最大增益誤差、2 mV 的最大偏置誤差和保證的單調(diào)性。它們提供 LFCSP (3-mm × 3-mm) 和 TSSOP 封裝,并且 4-kV ESD 額定值突顯了它們具有極其強大的性能。DAC 輸入可通過 1.8 V SPI 兼容接口進行編程。上電復(fù)位電路會確保 DAC 輸出電源最多為 0 V,并且保持此狀態(tài),直到進行有效的寫入。復(fù)位引腳允許進行異步復(fù)位?;鶞?zhǔn)電壓源輸出引腳允許在外部將片內(nèi)基準(zhǔn)電壓源用作系統(tǒng)基準(zhǔn)電壓源。菊花鏈功能可以實現(xiàn)具有更多通道數(shù)量的系統(tǒng)。外部基準(zhǔn)電壓源型 AD5686/AD5685/AD5684 允許以最低的成本在所有通道上共用單個基準(zhǔn)電壓源。圖 3 顯示了多通道系統(tǒng)中使用這些 DAC 的部分。

圖 3. 系統(tǒng)框圖部分顯示了由 Blackfin DSP 控制的 AD5686R 和 AD5686。

電壓切換式 16 位 DAC 提供低噪聲、快速設(shè)置和更佳線性度

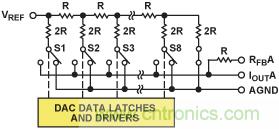

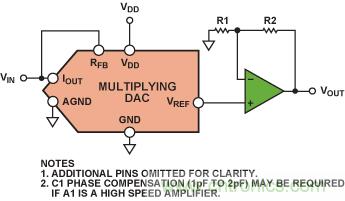

電阻梯式乘法 DAC 基于改變游戲規(guī)則的 10 位 CMOS AD7520—大約 40 年前推出—最初與反相運算放大器配合使用,并且提供了便于虛擬接地的放大器求和點 (IOUTA)(圖 4)。

圖 4. CMOS 乘法 DAC 架構(gòu)。

然而,它們還可以在少數(shù)情況下用于那些提供同相電壓輸出的電壓切換式配置中,并將運算放大器用作電壓緩沖器(圖 5)。在這里,基準(zhǔn)電壓 VIN 應(yīng)用于 IOUT,并且輸出電壓 VOUT 可在 VREF 處提供。不久會推出針對此目的優(yōu)化的 12 位版本。

圖 5. 電壓切換模式下的乘法 DAC。

快速發(fā)展到現(xiàn)在:隨著單電源系統(tǒng)越來越普遍,設(shè)計師面臨的挑戰(zhàn)是如何在更高電壓下盡力保持出色的性能水平,同時保持對功耗的控制。能夠在此模式下使用的、具有更高分辨率(多達(dá)16 位)的器件受到了市場的更多青睞。

在電壓切換模式下使用乘法 DAC 的明顯好處是不會發(fā)生任何信號反相,因此正基準(zhǔn)電壓會產(chǎn)生正輸出電壓。但在這種模式下使用時,R-2R 梯形架構(gòu)也存在缺點。與在電流控制模式下使用相同的 DAC 相比,與 R-2R 梯形網(wǎng)絡(luò)串聯(lián)使用的 N 通道開關(guān)的非線性電阻會降低積分非線性 (INL)。

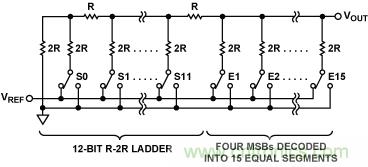

AD5541A 等新型高分辨率 DAC(如圖 6 所示)已經(jīng)開發(fā)出來,旨在克服乘法 DAC 的局限性,同時保持電壓切換的優(yōu)勢。通過使用部分分段的 R-2R 梯形網(wǎng)絡(luò)和輔助開關(guān),AD5541A 在 16 位分辨率下提供 ±1-LSB 的精度,而且無需調(diào)整整個指定溫度范圍(−40°C 至 +125°C)、11.8 nV/√Hz 噪聲和 1-µs 建立時間。

圖 6. AD5541A 架構(gòu)。

性能特性

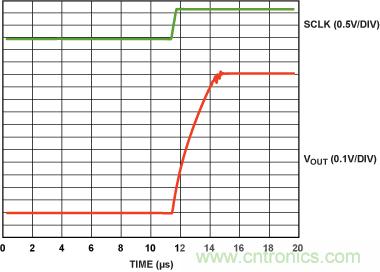

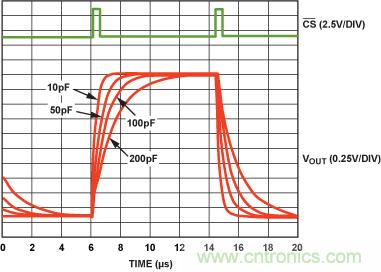

建立時間:圖 7 和圖 8 比較了處于電壓模式下的乘法 DAC 和 AD5541A 的各自建立時間。當(dāng)輸出上的容性負(fù)載減至最低時,AD5541A 的建立時間約為 1 µs。

圖 7. 乘法 DAC 建立時間。

圖 8. AD5541A 建立時間。

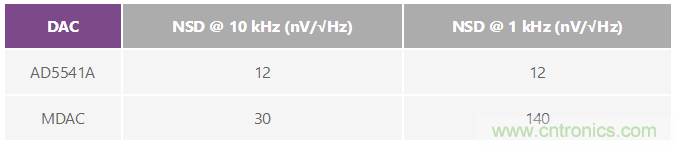

噪聲譜密度:表 1 比較了 AD5541A 和乘法 DAC 的噪聲譜密度。AD5541A 在 10 kHz 時的性能略微好于乘法 DAC,但在 1 kHz 時的性能遠(yuǎn)遠(yuǎn)勝出乘法 DAC。

表 1. AD5541A 和乘法 DAC 的噪聲譜密度對比

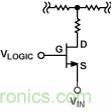

積分非線性:積分非線性 (INL) 用于測量 DAC 的理想輸出與在去除增益和偏置誤差之后的實際輸出之間的最大偏差。與 R-2R 網(wǎng)絡(luò)串聯(lián)使用的開關(guān)會影響 INL。乘法 DAC 一般采用 NMOS 開關(guān)。在電壓切換模式下使用時,NMOS 開關(guān)的來源連接到基準(zhǔn)電壓,漏極連接到梯形網(wǎng)絡(luò),并且柵極由內(nèi)部邏輯驅(qū)動(圖 9)。

圖 9. 乘法 DAC 開關(guān)。

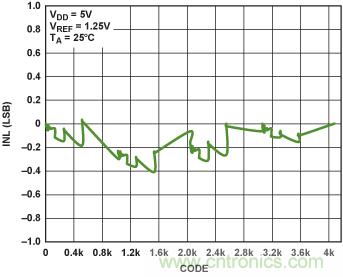

為了使電流流入 NMOS 器件,VGS 必須大于閾值電壓 VT。在電壓切換模式下,VGS = VLOGIC – VIN 必須大于 VT = 0.7 V。

乘法 DAC 的 R-2R 梯形網(wǎng)絡(luò)經(jīng)過專門設(shè)計,可以通過每個支腿均勻分配電流。這要求整體接地電阻(從每個支腿的頂部查看)必須完全相同。這可通過調(diào)整開關(guān)的小大來完成(每個開關(guān)的大小與其導(dǎo)通電阻成正比)。如果一個支腿中的電阻發(fā)生了變化,流過此支腿的電流將會改變,進而導(dǎo)致線性誤差。VIN 不能太大,否則會關(guān)閉開關(guān),但它必須大到足以將開關(guān)電阻保持在較低的水平,因為 VIN 的變化會影響 VGS,進而導(dǎo)致導(dǎo)通電阻發(fā)生非線性變化,如下所示:

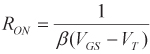

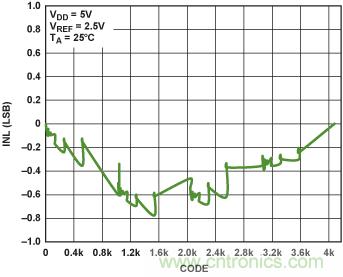

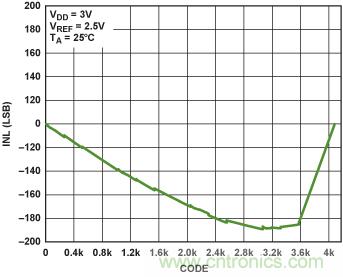

這種導(dǎo)通電阻的變化會使電流失衡并降低線性度。因此,乘法 DAC 的電源電壓不能減少太多。反過來,為了保持線性度,基準(zhǔn)電壓不應(yīng)比 AGND 高出 1 V 以上。通過使用 5 V 電源,當(dāng)從 1.25 V 基準(zhǔn)電壓源移至 2.5 V 基準(zhǔn)電壓源時,線性度開始降低,如圖 10 和 11 所示。 當(dāng)電源電壓降低到 3 V 時,線性度完全消失,如圖 12 所示。

圖 10. IOUT 乘法 DAC 的 INL,反向模式,VDD = 5 V,VREF = 1.25 V。

圖 11. IOUT 乘法 DAC 的 INL,反向模式,VDD = 5 V,VREF = 2.5 V。

圖 12. 乘法 DAC 的 INL,反向模式,VDD = 3 V,VREF = 2.5 V。

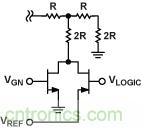

為盡可能減少此影響,AD5541A 采用了互補 NMOS/PMOS 開關(guān),如圖 13 所示?,F(xiàn)在,開關(guān)的總導(dǎo)通電阻來自 NMOS 和 PMOS 開關(guān)的并聯(lián)電阻。如前所述,NMOS 開關(guān)的柵極電壓由內(nèi)部邏輯控制。內(nèi)部產(chǎn)生的電壓 VGN 會設(shè)置理想的柵極電壓,以平衡 NMOS 的導(dǎo)通電阻與 PMOS 的導(dǎo)通電阻。開關(guān)的大小會調(diào)整以與代碼成比例,因此導(dǎo)通電阻將會與代碼成比例。這樣,電流將會調(diào)整,并且精度將得以保持。當(dāng)基準(zhǔn)輸入檢測到隨代碼變化的阻抗時,它將由低阻抗源驅(qū)動。

圖 13. 互補 NMOS/PMOS 開關(guān)。

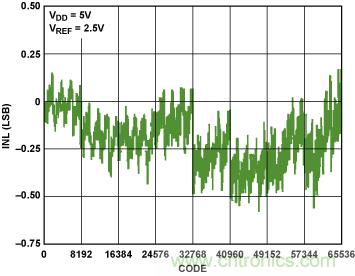

圖 14 和 15 顯示了采用 5 V 和 2.5 V 基準(zhǔn)電壓源的 AD5541A 的 INL 性能。

圖 14. AD5541A 的 INL,VDD = 5.5 V,VREF = 5 V。

圖 15. AD5541A 的 INL,VDD = 5.5 V,VREF = 2.5 V。

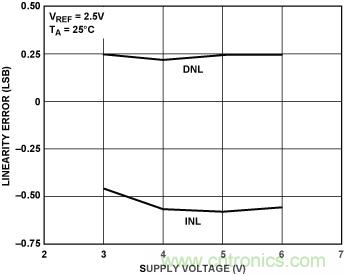

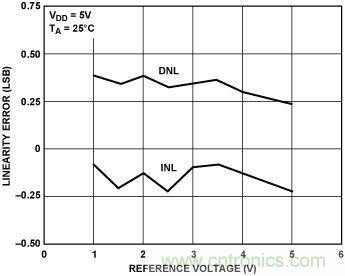

圖 16 和圖 17 顯示線性度在寬泛的基準(zhǔn)和電源電壓范圍內(nèi)變化很小。DNL 的性能表現(xiàn)與 INL 類似。AD5541A 線性度在溫度和電源電壓上指定;基準(zhǔn)電壓可以在 2.5 V 和電源電壓之間變化。

圖 16. AD5541A INL 和電源電壓對比。

圖 17. AD5541A INL 和基準(zhǔn)電壓對比。

關(guān)于 AD5541A 的更多信息

AD5541A 串行輸入、單電源、電壓輸出 nanoDAC+ 數(shù)模轉(zhuǎn)換器可以提供 16 位分辨率,并且具有 ±0.5-LSB 的典型積分和差分非線性。它非常適用于那些在電壓切換模式下使用乘法 DAC 的應(yīng)用場合。它在溫度和電源電壓上都表現(xiàn)良好,取得優(yōu)異的線性度,并且可用于需要精密直流性能和快速建立時間的 3 V 至 5 V 系統(tǒng)。通過使用范圍介于 2 V 和電源電壓之間的外部基準(zhǔn)電壓,未經(jīng)緩沖的電壓輸出可在 0 V 到 VREF 的范圍內(nèi)驅(qū)動 60 k? 的負(fù)載。該器件提供 1-µs 的建立時間(½ LSB)、11.8 nV/√Hz 的噪聲以及低故障率,非常適合部署在眾多不同的醫(yī)療、航空航天、通信和工業(yè)應(yīng)用領(lǐng)域中。它的 3 線、低功率 SPI 兼容串行接口可以處理高達(dá) 50 MHz 的時鐘輸入信號。AD5541A 采用單個 2.7 V 至 5.5 V 電源,吸入電流僅為 125 µA。它提供 8 引腳和 10 引腳 LFCSP 以及 10 引腳 MSOP 封裝,工作溫度范圍為 –40°C 至 +125°C,起價為 6.25 美元(1000 件)。

高速電流輸出 DAC 緩沖器

由于不會增加噪聲或消耗功率,變壓器通常被認(rèn)為是將高速電流輸出 DAC 的互補輸出轉(zhuǎn)換成單端電壓輸出的最佳選擇。雖然變壓器對高頻信號操作良好,但是它們不能處理許多儀表和醫(yī)療應(yīng)用所需的低頻信號。這些應(yīng)用場合需要使用低功率、低噪聲和高速放大器以將互補電流轉(zhuǎn)換成單端電壓。下面介紹的三個電路均可接受來自 DAC 的互補輸出電流并提供單端輸出電壓。后兩個電路的失真與變壓器解決方案進行了對比。

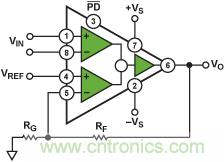

差分放大器:AD8129 和 AD8130 差分-單端放大器(圖 1)用于第一個電路(圖 2)。對于高頻信號,它們具有極高的共模抑制能力。AD8129 對 10 以上的增益是穩(wěn)定的,AD8130 則是單位增益穩(wěn)定。其用戶可調(diào)的增益可以通過兩個電阻 RF 和 RG 的比率進行設(shè)置。無論增益如何設(shè)置,AD8129 和 AD8130 的引腳 1 與引腳 8 上均具有非常高的輸入阻抗。基準(zhǔn)電壓(VREF,引腳 4)可以用于設(shè)置偏置電壓,然后將它乘以與差分輸入電壓相同的增益。

圖 1. AD8129/AD8130 差分放大器。

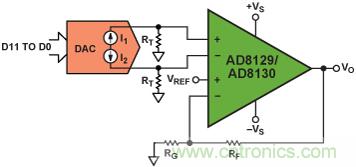

圖 2. 使用 AD8129/AD8130 的 DAC 緩沖器。

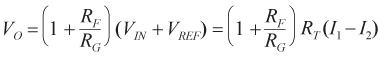

方程式 1 和 2 顯示了放大器的輸出電壓與 DAC 的互補輸出電流之間的關(guān)系。終端電阻 RT 執(zhí)行電流至電壓的轉(zhuǎn)換;RF 和 RG 的比率決定增益的大小。在方程式 2 中,VREF 設(shè)置為 0。

(2)

(2)在圖 2 中,此電路采用了四通道、高速、低功耗 14 位 DAC,在此,互補電流輸出級增加了低功耗 DAC 的速度并減小了低功耗 DAC 的失真。

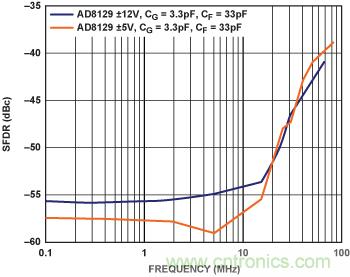

圖 3 顯示了在兩個電源電壓值下使用 DAC 和 AD8129 時的無雜散動態(tài)范圍 (SFDR),該范圍作為頻率的函數(shù),并且 RF = 2 k?,RG = 221 ?,RT = 100 ?,VO = 8 V p-p。之所以在這里選擇 AD8129,是因為它可以提供較大的輸出信號、對 G = 10 穩(wěn)定并且比 AD8130 具有更高的增益帶寬積。在兩種情況下,SFDR 通常均優(yōu)于 55 dB,超過 10 MHz,并且在較低電源電壓下改善了大約 >3 dB 。

圖 3. DAC 和 AD8129 的失真(VO = 8 V p-p)。

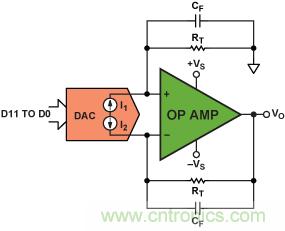

單位增益運算放大器:第二個電路(圖 4)使用包含兩個 RT 電阻的高速放大器。放大器可以簡單地通過 RT 將互補電流 I1 和 I2 轉(zhuǎn)換成單端輸出電壓 VO。這一簡單的電路不允許將放大器用作增益模塊進行信號放大。

圖 4. 使用運算放大器的簡單差分-單端轉(zhuǎn)換器。

方程式 3 顯示了 VO 和 DAC 輸出電流之間的關(guān)系。失真數(shù)據(jù)通過與 RT 并聯(lián)的 5 pF 電容器進行測量。

為了展示此電路的性能,DAC 與 ADA4857 和 ADA4817 運算放大器搭配使用,并且 RT = 125 ?(CT = CF = 5 pF,與 RT 并聯(lián),以實現(xiàn)穩(wěn)定性和低通濾波)。單 ADA4857-1 和雙 ADA4857-2 是單位增益穩(wěn)定、高速、電壓反饋型放大器,具有低失真、低噪聲和高壓擺率。作為超聲、ATE、有源濾波、ADC 驅(qū)動器等各種應(yīng)用的理想解決方案,它具有 850 MHz 帶寬、2800 V/μs 壓擺率和 10 ns 建立時間(0.1%)—所有均采用 5 mA 的靜態(tài)電流工作。憑借寬泛的電壓范圍(5 V 至 10 V),ADA4857-1 和 ADA4857-2 成為那些要求寬動態(tài)范圍、出色精度、高速和低功耗的系統(tǒng)的理想選擇。

單 ADA4817-1 和雙 ADA4817-2 FastFET ™ 放大器是單位增益穩(wěn)定、超高速度、電壓反饋型運算放大器,具有 FET 輸入。它們基于 ADI 專有的超快速互補雙極型工藝 (XFCB) 開發(fā),具有超低的噪聲(4 nV/√Hz 和 2.5 fA/√Hz)和非常高的輸入阻抗。憑借 1.3 pF 的輸入電容、2 mV 的最大偏置電壓、低功耗 (19 mA) 和寬泛的 −3 dB 帶寬 (1050 MHz),它們成為數(shù)據(jù)采集前端、光電二極管前置放大器和其他寬帶跨阻抗應(yīng)用場合的理想之選。它們具有 5 V 至 10 V 的電源電壓范圍和單或雙電源工作能力,適合在有源濾波、ADC 驅(qū)動、DAC 緩沖等眾多應(yīng)用場合中工作。

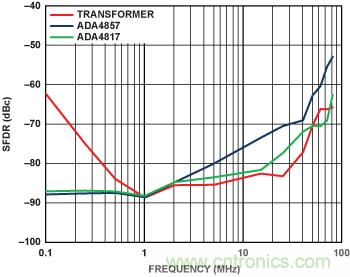

圖 5 比較了這一電路與使用變壓器的電路的失真和頻率( VO = 500 mV p-p)。變壓器的失真小于放大器,后者在高頻下具有更低的增益,但其失真在低頻下變得越來越差。從圖中看出,可在有限的范圍內(nèi)實現(xiàn)近 90 dB 的 SFDR,并且在 10 MHz 之前優(yōu)于 70 dB。

圖 5. DAC、ADA4857 和 ADA4817 的失真(VO = 500 mV p-p,RL = 1 k?)。

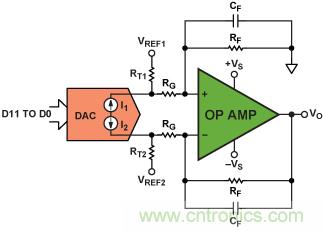

具有增益能力的運算放大器:第三個電路(圖 6)也使用了相同的高速運算放大器,但它包含一個將放大器與 DAC 隔離的電阻網(wǎng)絡(luò),這允許設(shè)置增益,并可以靈活使用兩個基準(zhǔn)電壓(VREF1 和 VREF2)之一來調(diào)節(jié)輸出偏置電壓。

圖 6. 具有增益和偏置能力的差分-單端電路。

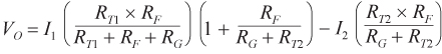

方程式 4 定義了在 VREF1 = VREF1 = 0 時 DAC 輸出電流和放大器輸出電壓之間的關(guān)系。為了匹配用于監(jiān)視 DAC 的放大器網(wǎng)絡(luò)的輸入阻抗,兩個終端電阻 RT1 和 RT2 必須單獨設(shè)置,同時考慮放大器的特性。

(4)

(4)圖 7 比較了此配置中放大器的失真以及變壓器電路的失真。RT1 = 143 ?,RT2 = 200 ?,RF = RG = 499 ?,CF = 5 pF—(實現(xiàn)穩(wěn)定性和高頻濾波),—以及 RL = 1 k?。從圖中看出,在高頻時,ADA4817 的性能與變壓器相當(dāng),并且在 70 MHz 之前始終優(yōu)于 −70 dBc SFDR。在低頻時,與變壓器相比,兩個運算放大器保持了卓越的保真度。

圖 7. DAC、ADA4817 和 ADA4857 的失真(VO = 500 mV p-p)。

本文通過比較電路在使用放大器和變壓器時的性能,展示了在將低失真、低噪聲、高速放大器用作 DAC 緩沖器時的一些優(yōu)點。它還比較了三個使用兩種不同放大器架構(gòu)的應(yīng)用電路,并且提供了在使用 DAC 和 AD8129、ADA4857-1/ADA4857-2 以及 ADA4817-1/ADA4817-2 放大器時的測量數(shù)據(jù)示例。數(shù)據(jù)表明,在頻率小于 1 MHz 時,放大器的性能優(yōu)于變壓器,并且在 80 MHz 之前,放大器的性能接近變壓器的性能。在功耗和失真之間做出取舍時,放大器的選擇是非常重要的。

推薦閱讀: