【導讀】本文將透露世界首款K波段數(shù)據(jù)轉(zhuǎn)換器EV12DS460A背后的設(shè)計秘密���,介紹為了提高性能和規(guī)避CMOS設(shè)計限制而引入的超高速制程。同時本文也將解釋,緊湊的單核心數(shù)據(jù)轉(zhuǎn)換器核心配合仔細斟酌的設(shè)計如何讓EV12DS460A的性能有突破性提高。最后,您可以看到布線和電路簡化的細微差別是設(shè)計時應(yīng)考慮的重要因素���。

概述

微波系統(tǒng)設(shè)計師一直在追求更高的性能和更高的工作帶寬。簡化設(shè)計和降低功耗���、尺寸���、重量同樣是需考慮的問題���。UWB數(shù)據(jù)轉(zhuǎn)換器能極大地簡化多通道傳輸系統(tǒng)的設(shè)計(如果您對此不了解,請訪問這里)����。多年來,利用上述特性開發(fā)的器件不可勝數(shù)���。但是����,沒有任何一款器件有最新的數(shù)字模擬轉(zhuǎn)換器(DAC) EV12DS460的性能���。事實上,這款新型的DAC的帶寬能跨越高達微波K波段 26.5GHz的巨大頻譜范圍���。

在去年的歐洲微波IC會議上涌現(xiàn)了一些關(guān)于單片微波IC (MMIC) 的初步想法���。早期的技術(shù)信息表明這樣的產(chǎn)品能達到X波段(8到12GHz)的性能���。隨后,詳細的寬帶測試表明這款DAC的性能遠不止如此����。這款器件能工作在8個奈奎斯特區(qū)域,底噪極低����,雜散極少。

這款器件使人們窺見未來軟件定義微波系統(tǒng)(SDeMS)成為現(xiàn)實的可能性���。但是要實現(xiàn)這一目的����,有兩個重要的問題需回答:

1.使用什么技術(shù)達到如此高的性能���?

2.這款DAC的測試結(jié)果如何���?

本文將展示如何通過規(guī)避CMOS的設(shè)計限制和引入新的超高速制程實現(xiàn)強大的轉(zhuǎn)換能力,以及如何使用緊湊的單核數(shù)字轉(zhuǎn)換器配合仔細斟酌的電路設(shè)計實現(xiàn)性能的突破����。您將看到布線和電路簡化的細微差別是設(shè)計時應(yīng)考慮的重要因素���。首先,讓我們看看高層級架構(gòu)的選擇����。

高層級設(shè)計

決定性能的兩個要素分別是:

1.基本架構(gòu)

2.處理技術(shù)的速度

絕大多數(shù)的高速DAC使用時間交錯的多個核心來提高采樣率。但是����,這種方案在還原輸出信號時會遇到問題,難以避免產(chǎn)生信號雜散和由此導致的性能下降����。我們沒有使用交織DAC的方式,因為其SFDR性能很差����。我們使用分割式架構(gòu)設(shè)計這款DAC���。

分割式設(shè)計

基本的DAC設(shè)計���,可簡單理解成一系列的二進制權(quán)重電流源被連接到一個加法放大器。每個“2次方”的元素使能與否取決于相關(guān)的比特位置���。這種設(shè)計的優(yōu)點在于實現(xiàn)簡單���,只需有限的元素(每個比特1個)���。實際上,要線性放大超過8比特的源的難度極大����。

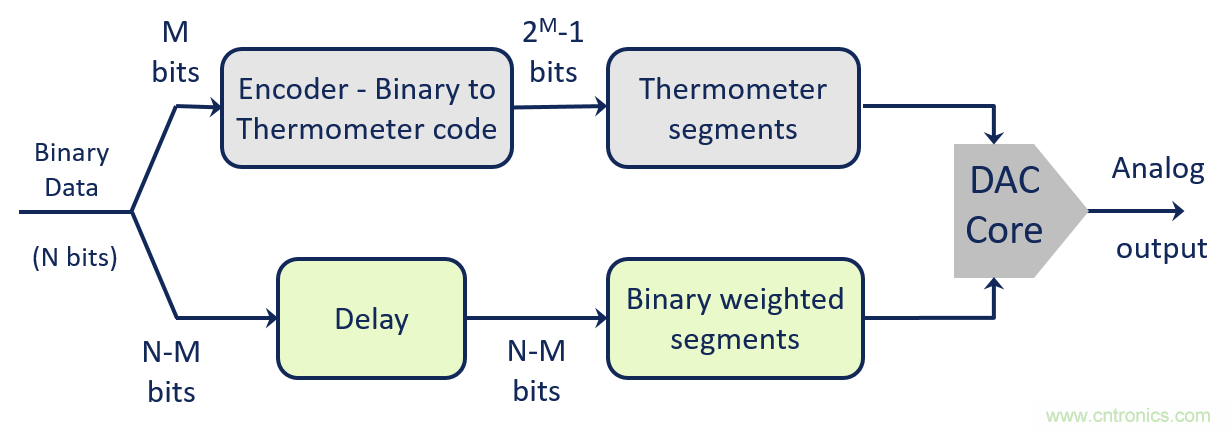

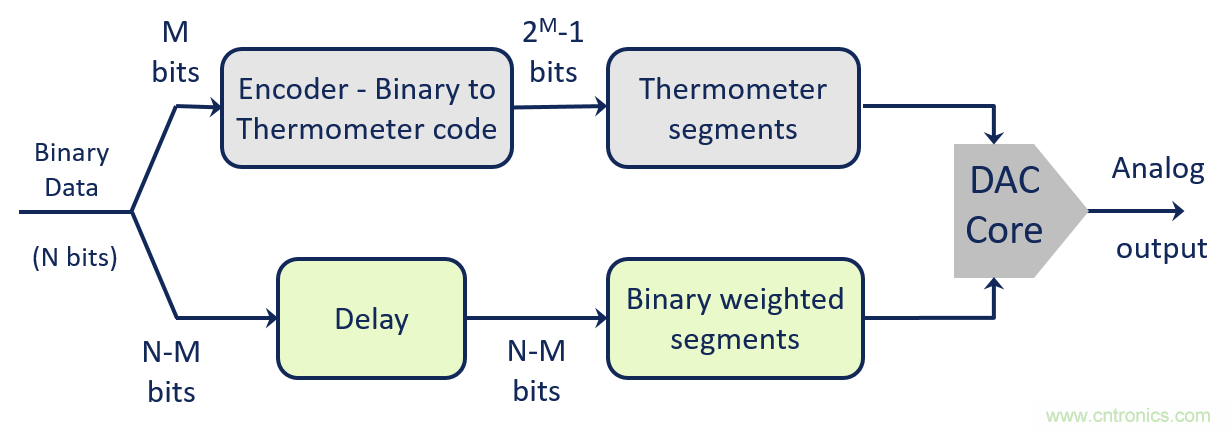

從架構(gòu)上來說,有一個簡單的方法實現(xiàn)單核心設(shè)計����。通過采用一種混合式分割設(shè)計(如圖1),分立的DAC把轉(zhuǎn)換任務(wù)分成一個m比特的編碼單元和一個2級(n-m)比特二進制權(quán)重單元����,處理LSB精度。編碼過程需要一些時間延遲���,在此之后上述兩個單元的輸出被綜合成最終的多比特轉(zhuǎn)換結(jié)果���。

圖1: EV12DS460A的混合式分割DAC架構(gòu)

如上文所述,要實現(xiàn)超過8bit的線性度難度極大,但是通過把多個比特的轉(zhuǎn)換分割成MSB和LSB單元���,則能夠大大降低核心的復(fù)雜度����。通過仔細的設(shè)計����,可以從同一個開關(guān)、電阻和電流源建立編碼單元和二進制權(quán)重單元���。

簡單的單核心設(shè)計

任何轉(zhuǎn)換器設(shè)計的起點是保證優(yōu)秀的靜態(tài)精度����。在混合式分割設(shè)計中����,精度由二進制權(quán)重LSB單元的誤差決定。

設(shè)計的目標是提高SFDR并且規(guī)避校準的操作����,達到優(yōu)于0.5LSB的性能。需考慮如下三點數(shù)據(jù)轉(zhuǎn)換器配置:

1.2比特編碼器(3段)加10比特權(quán)重段 = 13段

2.3比特編碼器(7段)加9比特權(quán)重段 = 16段

3.4比特編碼器(15段)加8比特權(quán)重段 = 23段

初步分析表明配置1是最佳的選擇���;它的段數(shù)最少����,因此核心區(qū)域最小���。但是���,它的靜態(tài)精度較差。要理解這一點����,請考慮12比特量化器能輸出滿福1V峰峰值,表明LSB量化電壓是244 µV (1Vp-p/4096)����。模擬實驗表明9比特權(quán)重段的匹配是125 µV。這比12比特0.5LSB的性能好兩倍���,保證單片DAC的工作����。但是���,因為權(quán)重選項是10比特���,無法進一步提高匹配的性能����,125 µV是物理性能的極限���,所以選項1是不可取的���。模擬實驗也表明選項3不可取,因為其對時鐘緩沖的動態(tài)載荷過大���。

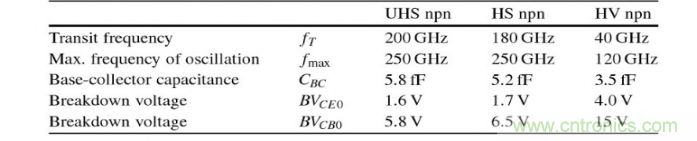

處理技術(shù)

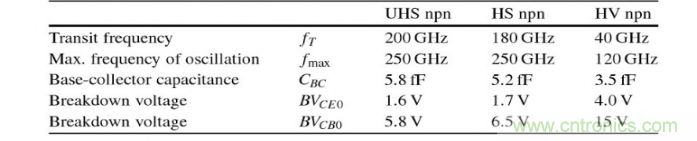

規(guī)避CMOS制程限制的設(shè)計使得轉(zhuǎn)換路徑更容易實現(xiàn)���。這種方案利用Infineon1異質(zhì)結(jié)硅鍺碳雙極型工藝實現(xiàn)較高的原始速度。通過引入NPN雙極型晶體管內(nèi)在固有的碳元素���,B7HF200工藝允許實現(xiàn)極薄的高度摻雜基極���。高轉(zhuǎn)化速度(200GHz Ft)和低阻抗基極是實現(xiàn)DAC高性能的兩個最重要的因素。

這種工藝已經(jīng)在高速和毫米波應(yīng)用中應(yīng)用了超過10年���,可用于多種固態(tài)微波器件���。

圖 2: B7HF200晶體管類型的比較

使用四層銅能夠進一步提高B7HF200的速度,適用于低電流密度的連接����。銅幫助降低寄生電流,此寄生電流是高速設(shè)計的夢魘����。

DAC設(shè)計的秘密

EV12DS460A的卓越性能并不是偶然得到的。自20112推出的較慢速的12bit產(chǎn)品以來����,這種架構(gòu)已經(jīng)進化了數(shù)代。即使是早期的產(chǎn)品���,性能也是非常優(yōu)秀的���,帶寬達到1.5GHz。

設(shè)計過程的重點在于3個通用的設(shè)計原則:

1.驅(qū)動量化器的動態(tài)載荷����,減少線長

2.保證工作穩(wěn)定

3.輸出脈沖整形����,減少畸變����,提高性能

驅(qū)動量化器的動態(tài)載荷

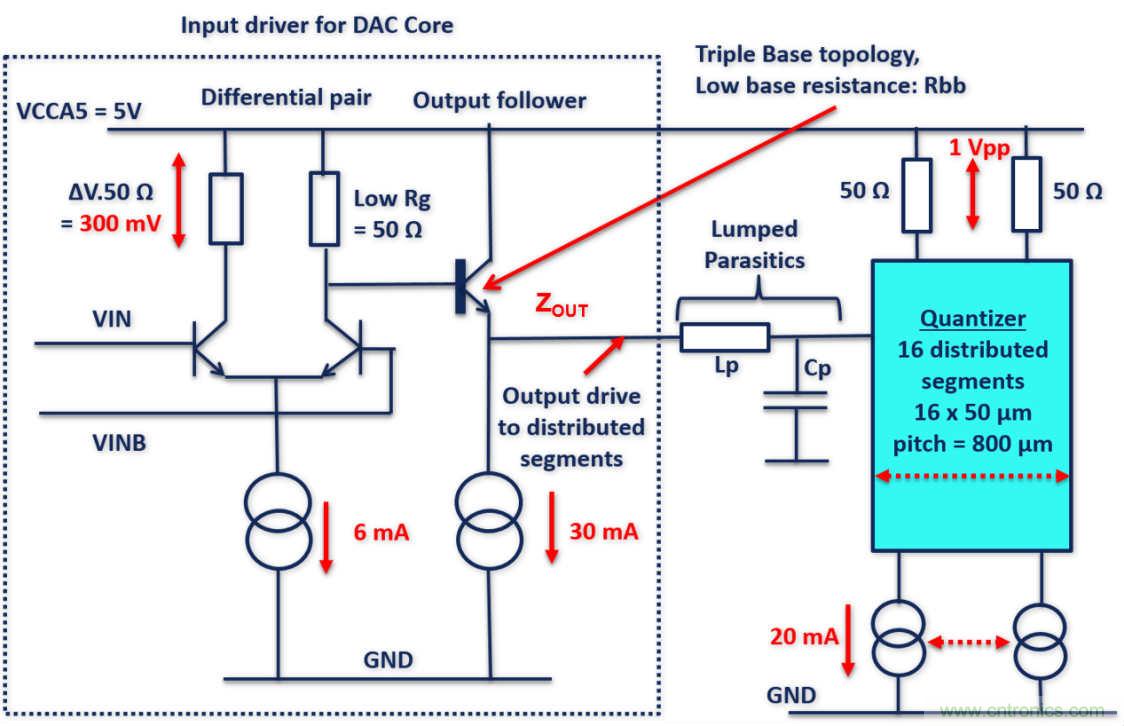

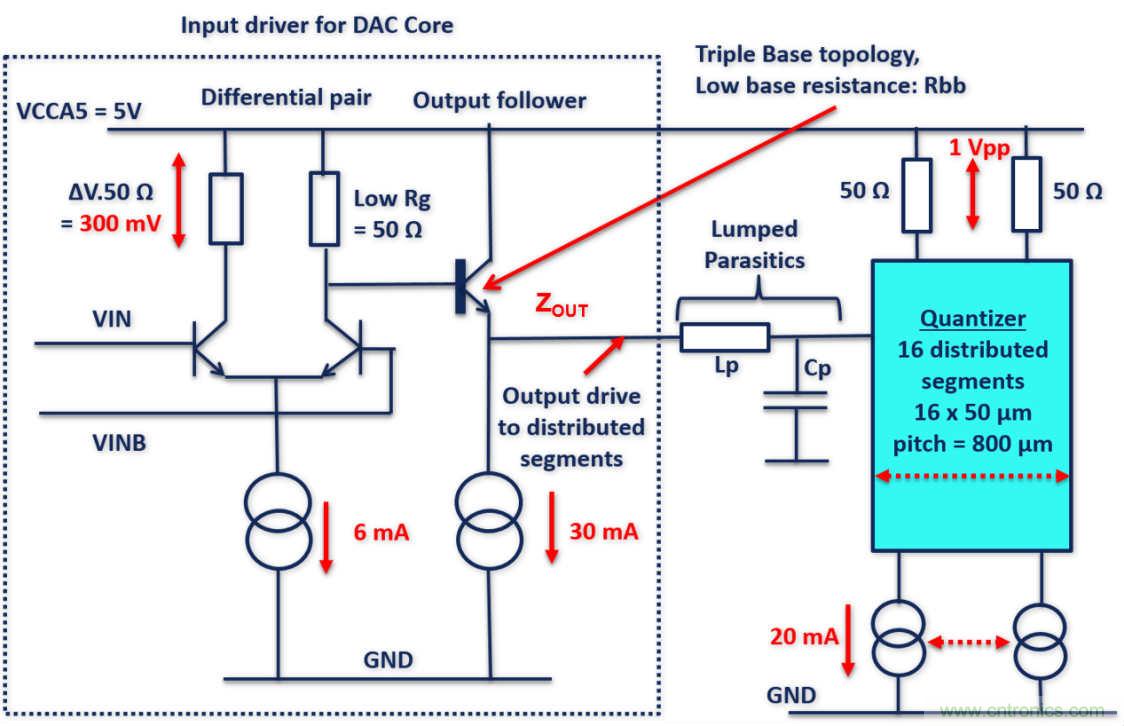

量化器的設(shè)計,部分是可以重用的(圖3)����。右邊是包含16個段的量化器,而左邊是采樣時鐘系統(tǒng)的模擬電路����。將它們組合起來,連接兩個電路的橋梁是芯片布線產(chǎn)生的Lp和Cp����。

圖3: 簡化EV12DS460A的輸入驅(qū)動

為了支持6到7Gsp的采樣率,時鐘源的抖動要低����,瞬變時間要短。當6Gsps采樣率時����,時鐘周期只有166ps���。保證干凈、快速的瞬變是確?��?焖倭炕筒蓸拥闹刂兄?��。但是���,在這個設(shè)計中����,相對高的量化器滿量程電流被設(shè)置成20mA���。為了快速驅(qū)動����,需要一個復(fù)雜的驅(qū)動器���,包含差分對和輸出電路����,其輸出阻抗非常低。

對于這個驅(qū)動器電路���,輸出阻抗Zout可以表示為:

Zout = (1/gm + Rbb + Rg)/Beta(f), 這里 gm 是晶體管跨導 (1/gm=1,25 ohms), Rbb 是輸出阻抗, Rg 是差分對的輸出阻抗���, Beta(f)是三極管的動態(tài)電流增益和頻率之間的關(guān)系。

考慮到B7HF200工藝的指標(截止頻率 fT = 200 GHz), 20GHz時的電流增益Beta(f) 等于10���。同時����,極低的雙極型晶體管的固有基極阻抗使Rbb 為25歐姆���。

Rg 也應(yīng)當是越小越好���,但是其不能太小,以避免過多地增大偏置電流����,導致功耗變大。大約50歐姆是比較合適的值���。

最后���,初步估算的輸出阻抗是: Zout = (1.25 + 25+ 50)/10 = ~ 7.5 ohms. 低輸出阻抗是器件快速工作的關(guān)鍵����。

為了維持輸出緩沖的300mV的脈沖幅度���,需要用300mV驅(qū)動50歐姆的終端 (300mV/50 = 6mA)���。 Rg 的進一步優(yōu)化會略微改善阻抗,但其代價是更高的功耗����。將 Rg減半����,偏置電流會上升到12mA。

減少線長����,保證DAC的穩(wěn)定性

下面將討論線長的重要性和它對高速設(shè)計的寄生效應(yīng)的影響。上述設(shè)計的每一個量化器段都只有50µm寬����,所以16段的總信號線長是800 µm (16 x 50 µm)����。減少線長是非常有用的���。

EV12DS460A的全局時間常數(shù)與如下三個因數(shù)有關(guān):

1.動態(tài)負載電容 (CL) 大約是 0.5 pF (CL=gm.Tf with gm = ΔI/ΔV = ~ 20mA/25mV .Tf 晶體管前向瞬變時間 = 0.8 ps)

2.金屬信號線的被動寄生電容(CP)大約是0.5 pF

3.金屬信號線的被動寄生電感 (LP)大約是 50 pH

在最壞的條件下����,全局時間常量ΣT可根據(jù)下式計算:

ΣT = Zout.CL + Zout.CP + LP/Zout, so ΣT = 7.5?. 0.5pF + 7.5 ?.500fF + 50pH/7.5 ? = 3.75 ps + 3.75 ps + 6.66 ps = ~14 ps

這個時間常量與DAC數(shù)據(jù)的35ps上升和下降時間 (tr/tf)有關(guān)����。而且,在這一層級上����,tr/tf 分別表示整個時鐘周期(166ps)的少于20%的時間,其能產(chǎn)生足夠快的時鐘邊沿����,支持10GHz的初步帶寬估算,達到DAC的設(shè)計目標����。

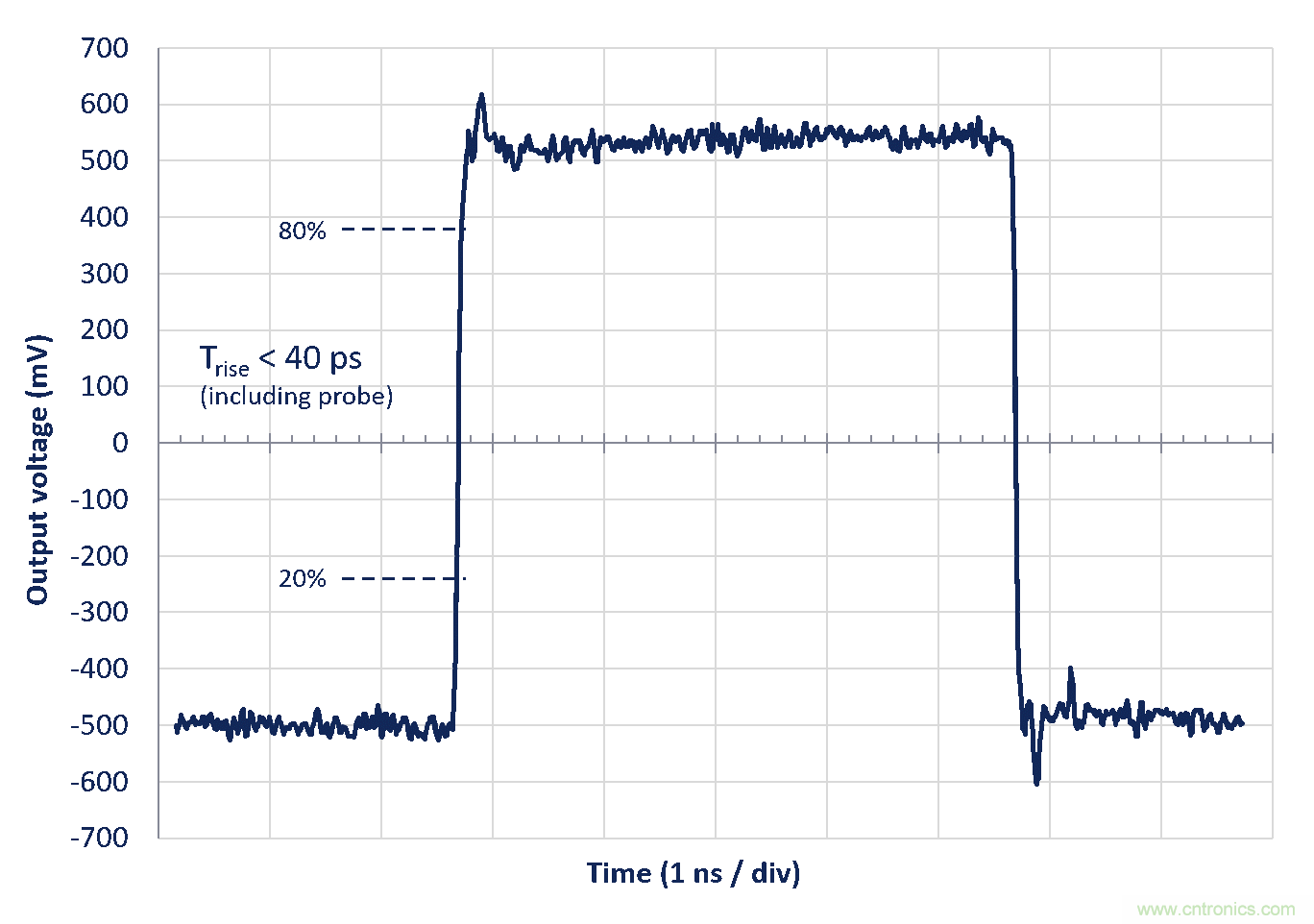

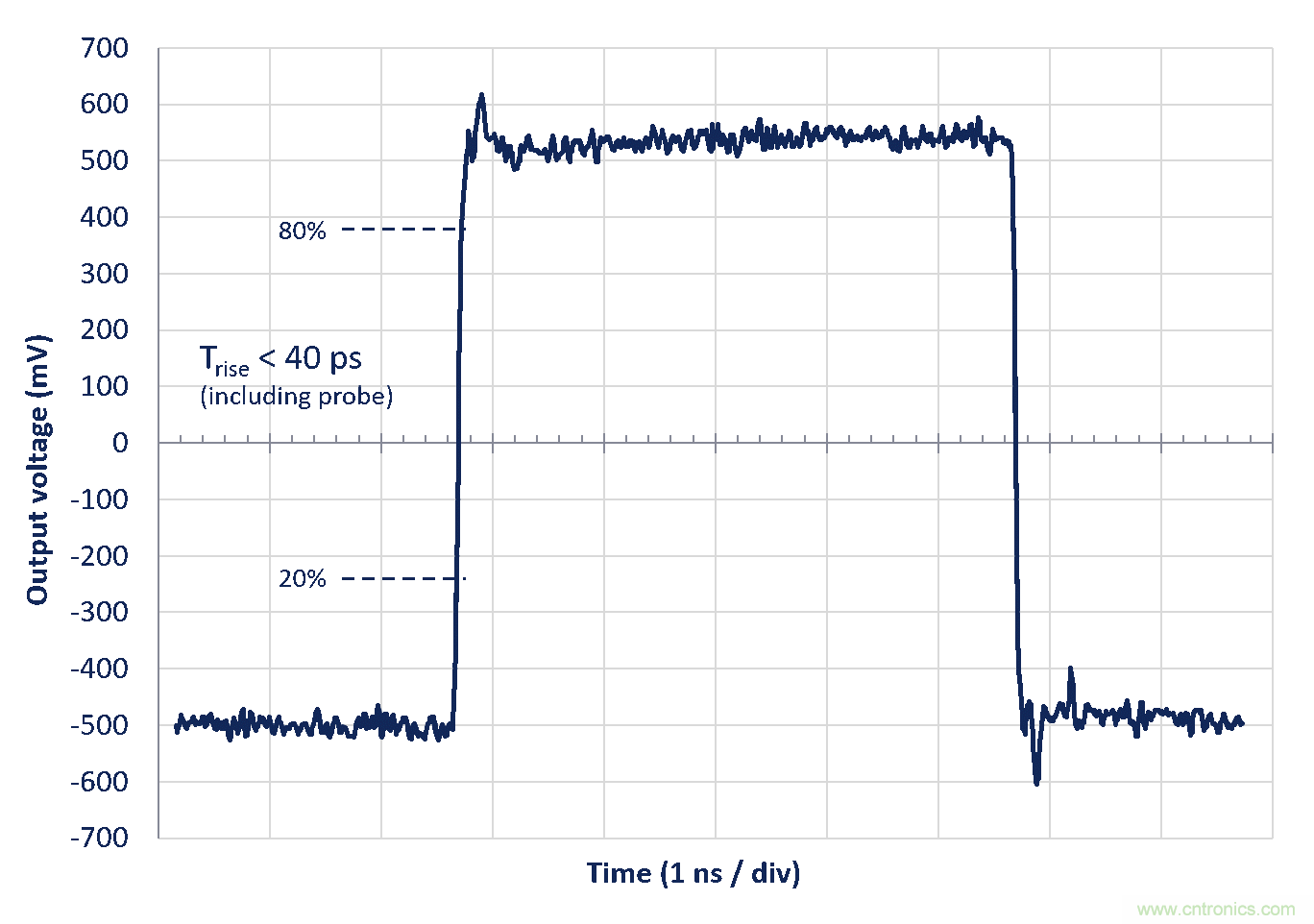

在初步的估算之外,我們使用一些特別的技術(shù)保證DAC的動態(tài)穩(wěn)定性。我們實現(xiàn)最大過沖(+4%)和最小回彈(-2%)的性能����。B7HF200工藝提供低阻抗的鍍銅技術(shù),幫助進一步調(diào)節(jié)和改善芯片的關(guān)鍵節(jié)點���。由此產(chǎn)生的優(yōu)異的性能(純凈的6GHz采樣)在圖4中以階躍響應(yīng)的形式表示���。

圖4: 加負載后30ps上升時間的階躍響應(yīng)

通過輸出脈沖整形提高動態(tài)性能

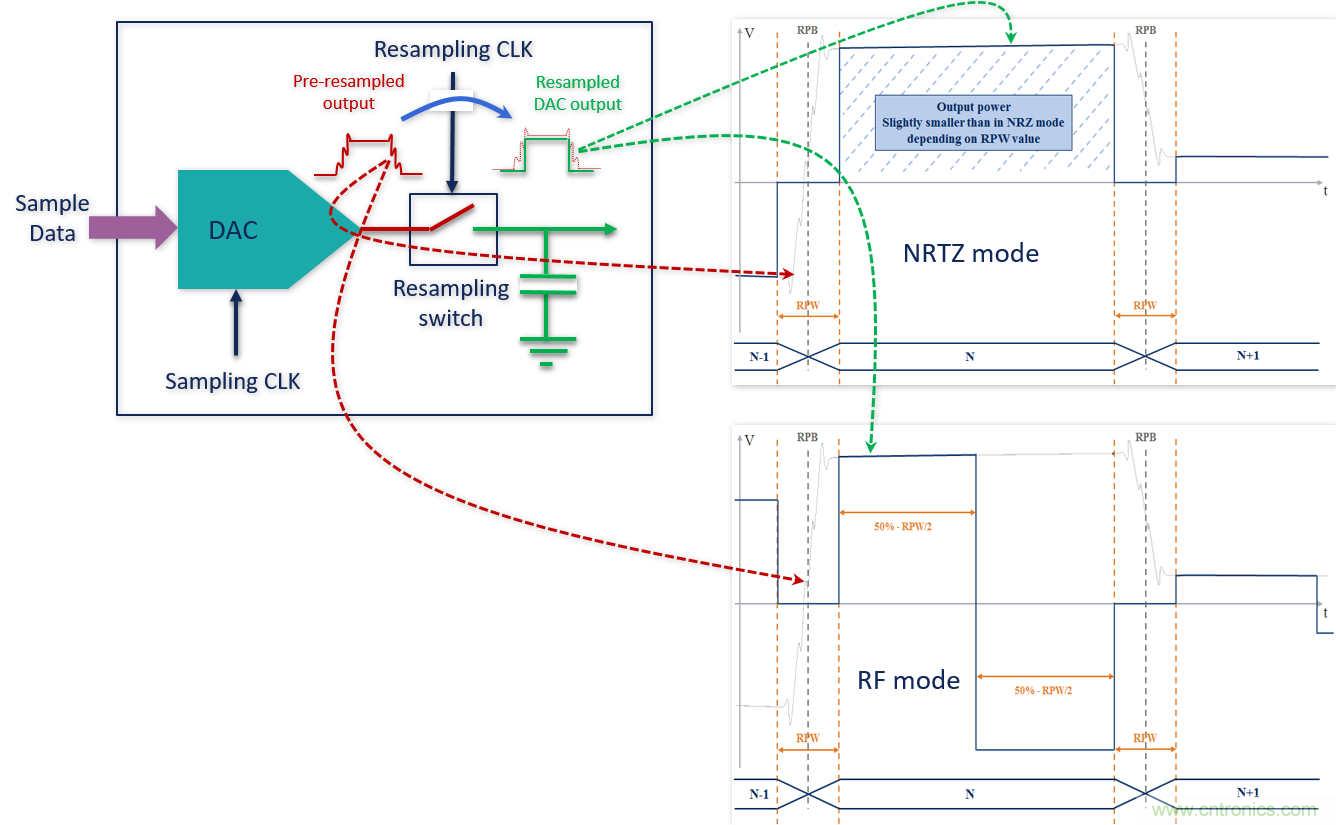

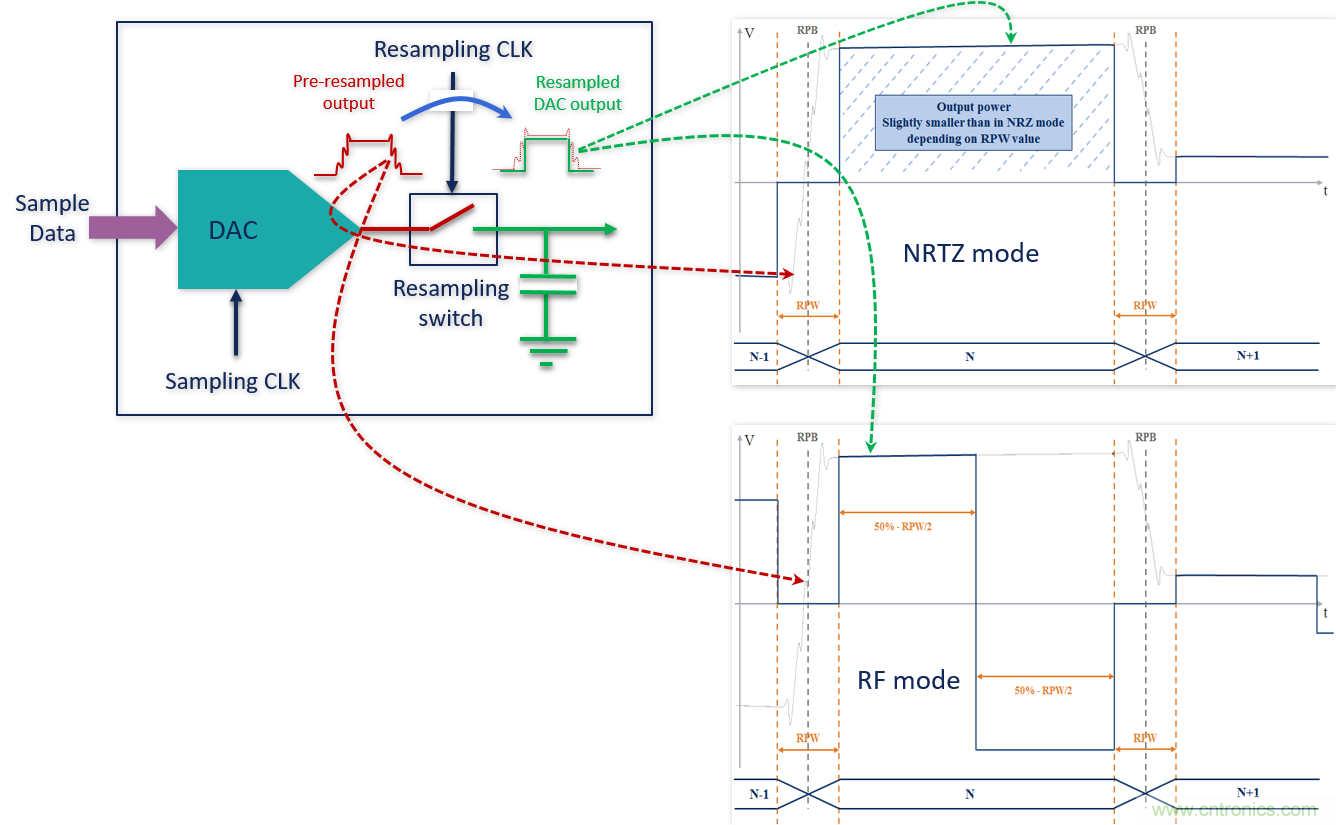

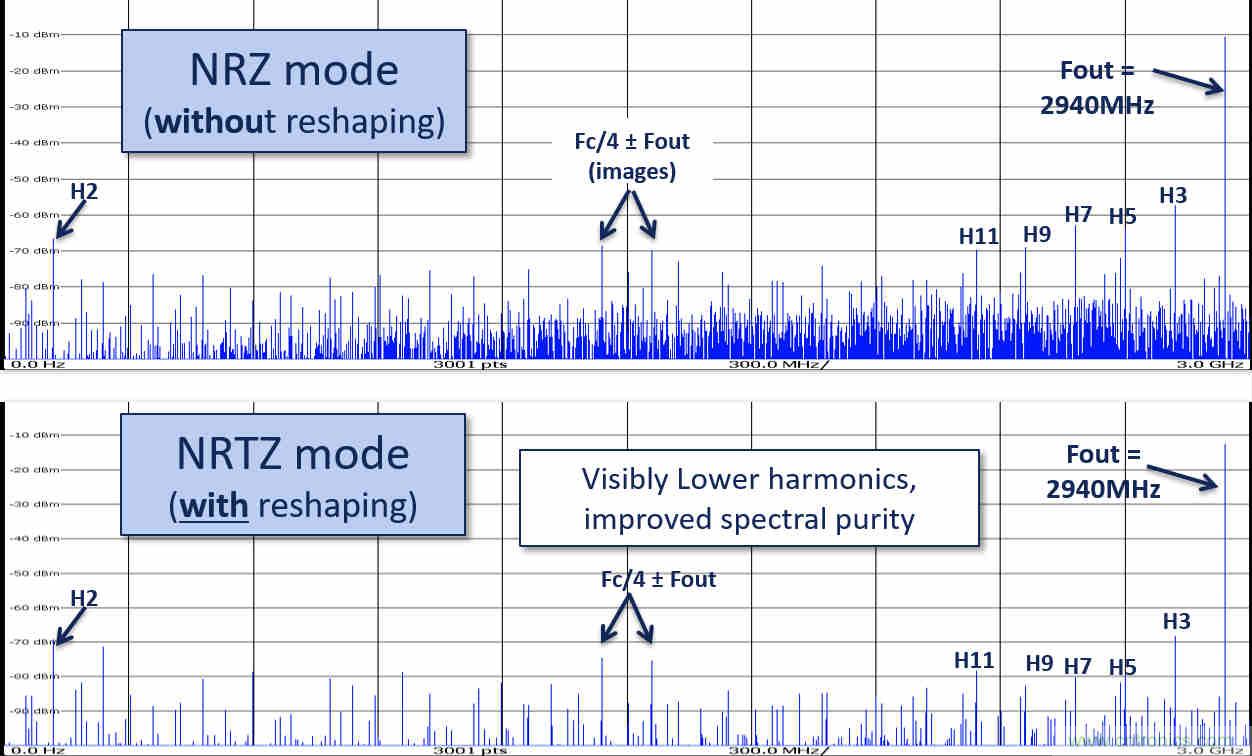

我們提供四種輸出脈沖整形模式(NRZ, NRTZ, RTZ, RF)以幫助系統(tǒng)設(shè)計師根據(jù)特定的輸出頻帶裁剪DAC的動態(tài)響應(yīng)性能,從而使設(shè)計更加便利���。大多數(shù)的量化器畸變與開關(guān)瞬變有關(guān)���。任何開關(guān)的毛刺都會疊加在最后的輸出信號上(圖5)。如果能夠移除這些毛刺����,輸出的頻譜純凈度將大大提高����。

圖5: DAC 脈沖整形的概念圖和NRTZ、RF模式的擴展波形

為了實現(xiàn)上述的脈沖整形����,我們在每個瞬變環(huán)節(jié)的邊緣之前強制把DAC輸出截止為0����,可以在NRTZ和RF模式的圖中看到輸出的波形����。脈沖整形通過3線串行接口控制,其有兩個用戶可控的參數(shù):整形脈沖寬度(RPW)和整形脈沖中心(RPB)����。如果所有的毛刺都被移除,脈沖中心必然與瞬變邊緣的中心一致���。注意���,這種技術(shù)犧牲了少量的輸出信號強度(與RPW定義的區(qū)域有關(guān))。

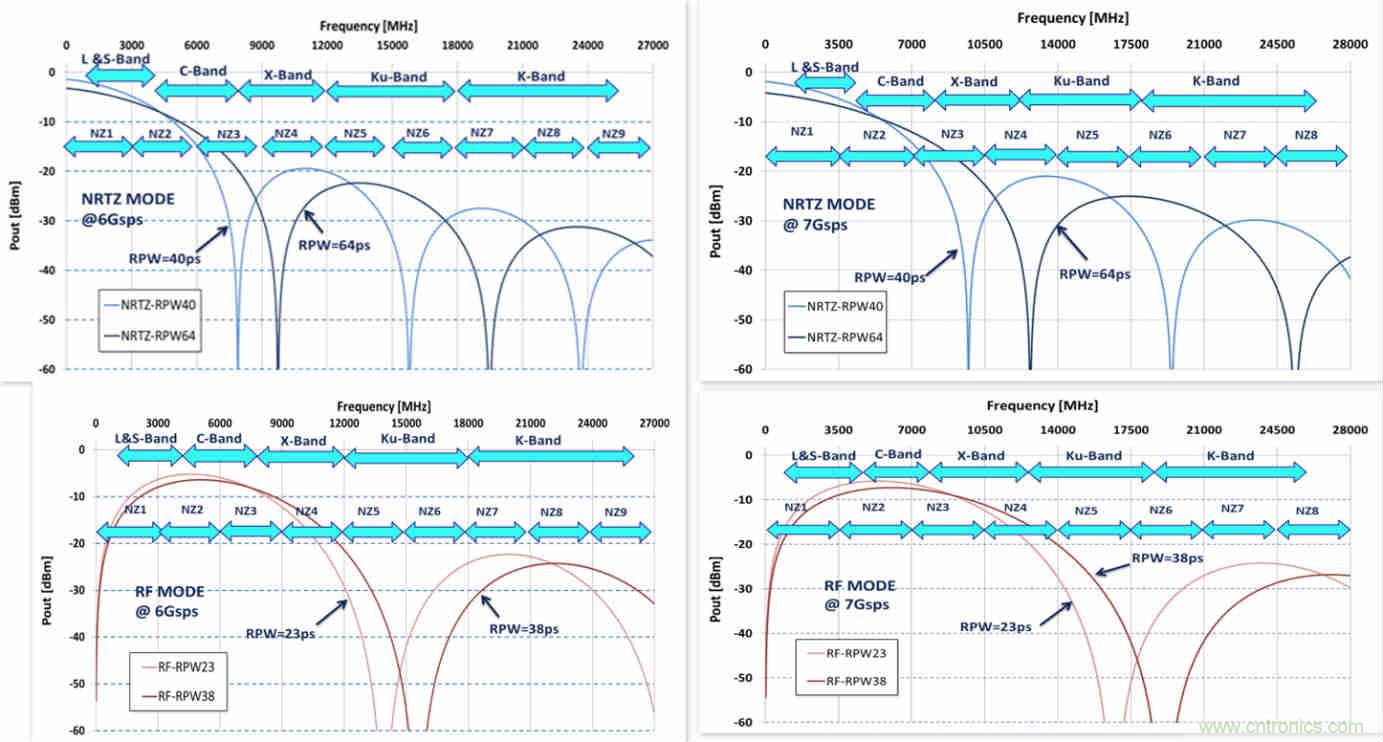

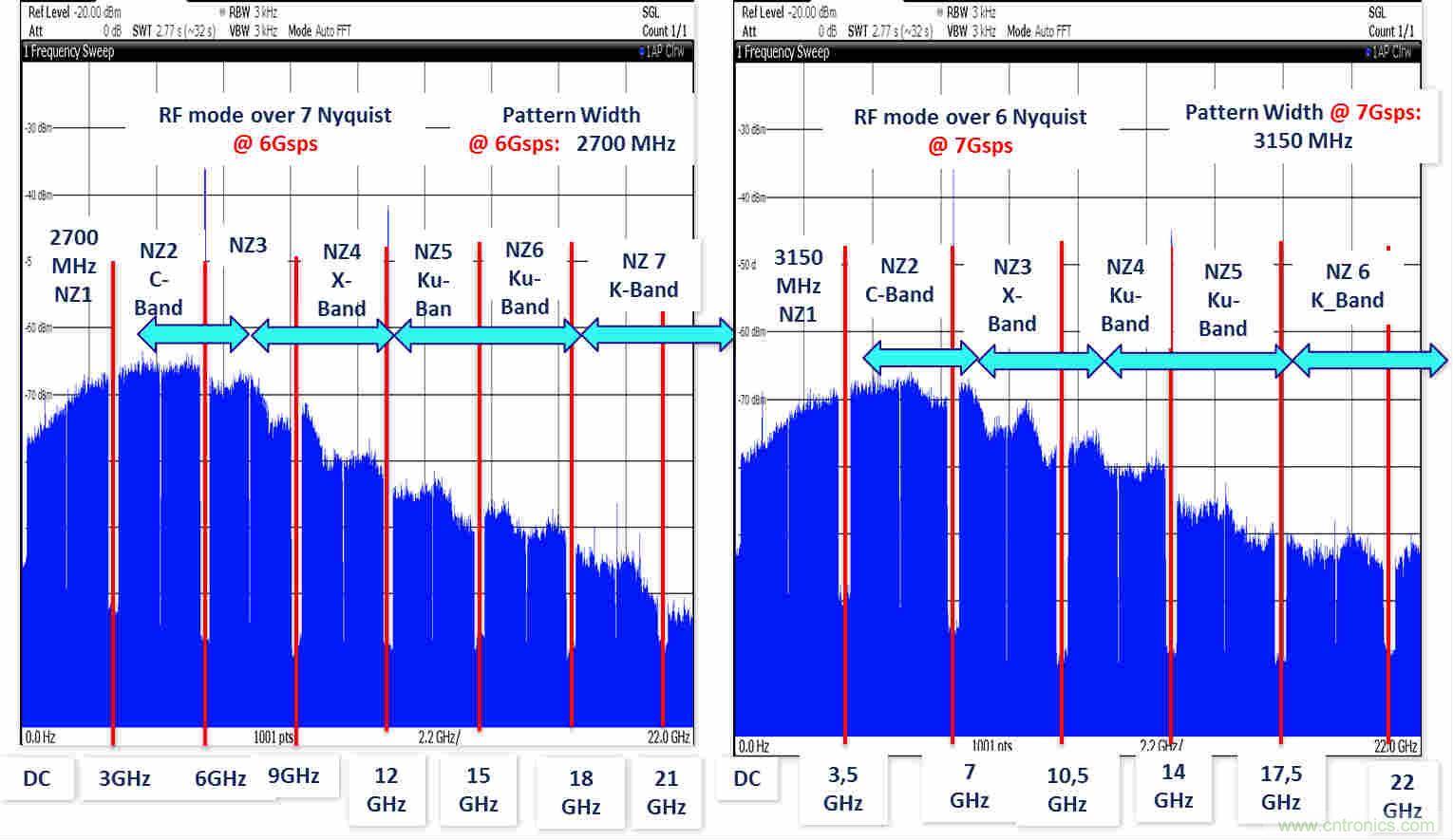

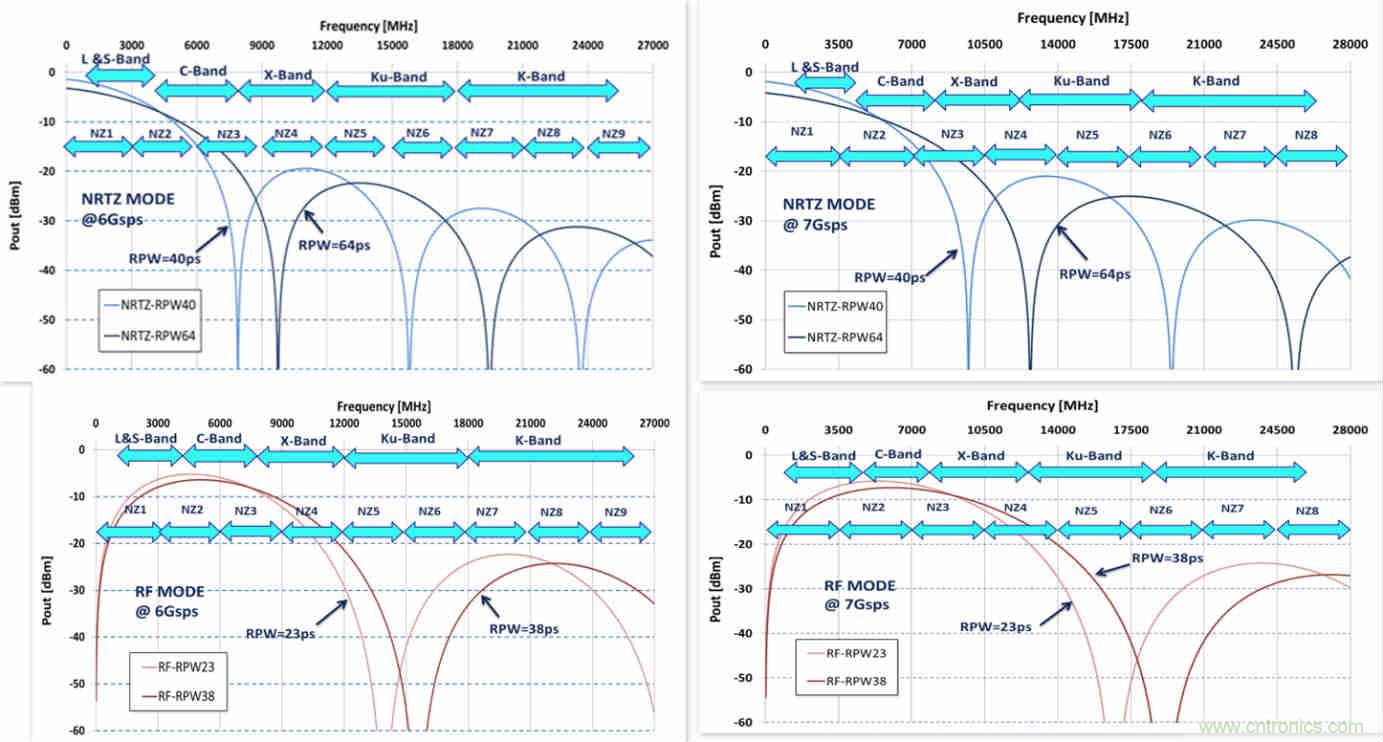

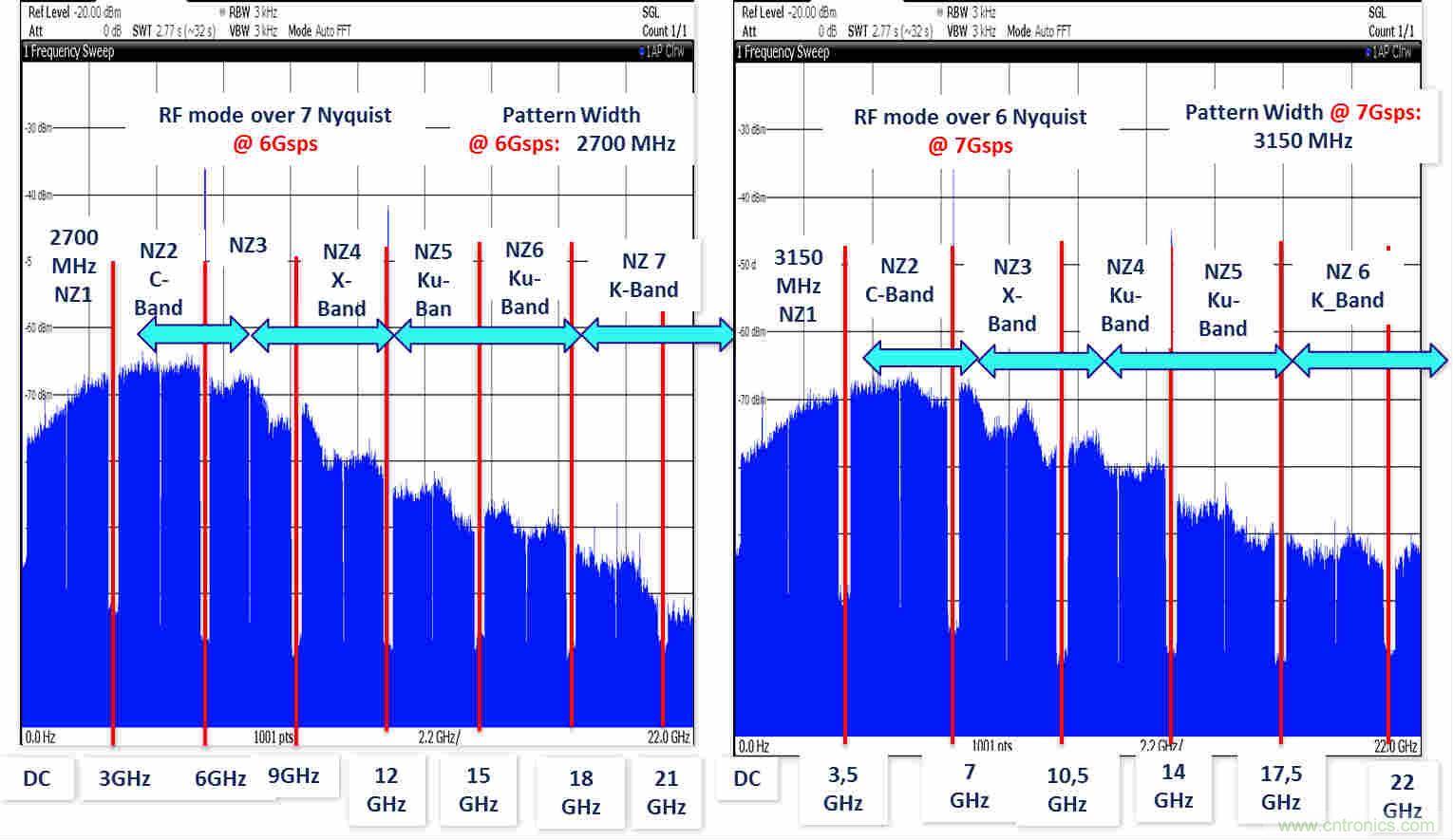

特性曲線(圖6)表明脈沖整形帶來的優(yōu)勢���。這些數(shù)據(jù)展示了兩種RPW設(shè)置(如果您對信號偏置不了解����,請閱讀這里)時橫跨8個奈奎斯特區(qū)間的高達27GHz (采樣率fs = 6 & 7Gsps)的頻譜���。注意采樣率的提高顯著地擴展了典型的SINC (sin(x)/x) DAC 輸出特性曲線����。

圖6: 兩種脈沖整形模式下DAC EV12DS460的輸出功率譜 (采樣率 6/7Gsps)

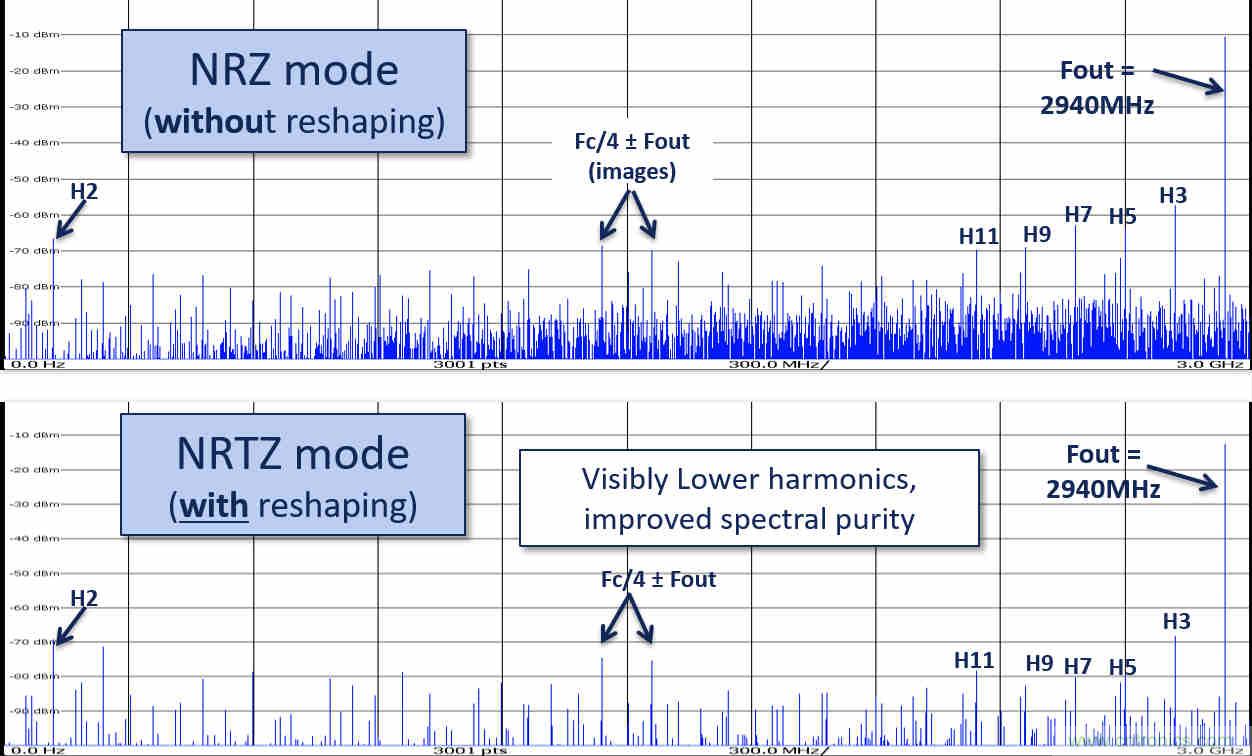

由于波形整形(H3從-57dBm提到到-69dBm),三次諧波的性能提高了+12dB����,極大地提高了DAC的性能。為了對比���,我們在6Gsps采樣率���,F(xiàn)out = 2940MHz的條件下使用有波形整形(NRTZ模式)和無波形整形(NRZ模式)產(chǎn)生如下的頻譜(圖7)。在NRTZ模式下����,波形整形帶來的性能提升非常明顯。

圖7: 6 GSps����,F(xiàn)out = 2940MHz時的單音頻譜���,有波形整形和無波形整形

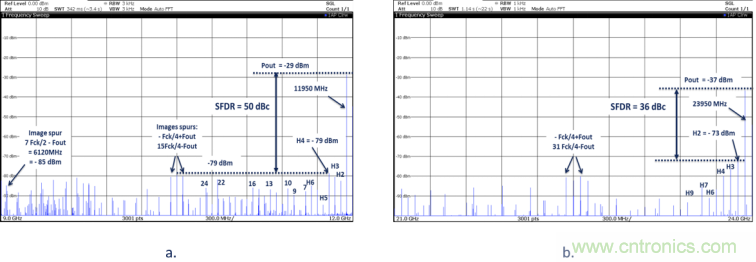

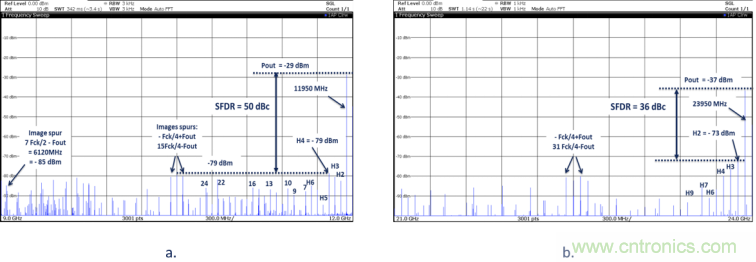

實測的性能

輸出3dB帶寬最大7GHz���,采樣率6Gsps保證產(chǎn)生3GHz的瞬時帶寬���。有用的輸出功率在X波段非常明顯(圖8a)。曲線表示一個第四奈奎斯特區(qū)間的11950MHz的單音載波���,SFDR為50dBc����。這里4次諧波主導SFDR����。這個載波頻譜是仔細選擇的,為了在X波段的邊沿����,使諧波信號更容易被觀察到,因為它們以自然的諧波順序出現(xiàn)����。

如果提高載波頻率到K波段(圖8),信號參考設(shè)置為在第8奈奎斯特區(qū)間的23950MHz���,2次諧波主導SFDR(-36.5dBc) ���。顯然����,諧波的純凈度有明顯提高����。

圖8: 11950 MHz 和 23950 MHz 處的SFDR

這些圖線還包含著其他突出的性能指標。每張圖里都展示了中頻點的非諧波雜散���。這些雜散與DAC 4:1輸入多路復(fù)用器的不完全混合信號抑制有關(guān)����。這些雜散的峰值在-80dBm����,相當好。DAC的底噪大約接近-110dBm����。

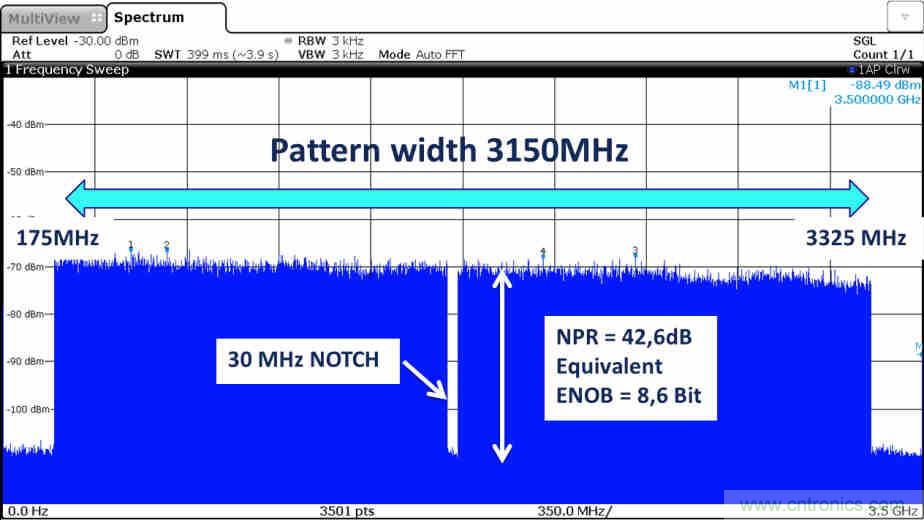

在實驗室里使用單音或多音的信號測試數(shù)據(jù)轉(zhuǎn)換器并不困難。這些測試的結(jié)果并不能完全表明DAC的性能����。當今的數(shù)據(jù)通信系統(tǒng)在大塊帶寬上部署復(fù)雜的模塊,所以我們需要更有效的寬帶測試方法���。這時噪聲功率比(NPR)非常有用���。它在一個較寬的帶寬上測試DAC,能表明信號如何包含多個非相干窄帶頻率����,以及它們在被DAC混合之時如何互相影響和互相干涉。顯然����,一款NPR指標接近理想n-bit器件的NPR指標的DAC是非常優(yōu)秀的寬帶器件。

NPR測試通常由一組高斯噪聲功率密度的數(shù)字譜實現(xiàn)����。對這個數(shù)字譜在頻域使用(數(shù)字)陷波濾波器將在感興趣的帶寬內(nèi)得到一個“安靜”的區(qū)域。然后把這個數(shù)字譜發(fā)送給DAC���,NPR的值通過計算陷波內(nèi)外的功率密度比的平均值得出����。對于一個理想的DAC����,陷波內(nèi)的信號功率只和量化噪聲有關(guān)����。而對于現(xiàn)實的DAC����,量化噪聲由熱噪聲、時鐘抖動帶來的噪聲和通道間交調(diào)帶來的噪聲有關(guān)����。

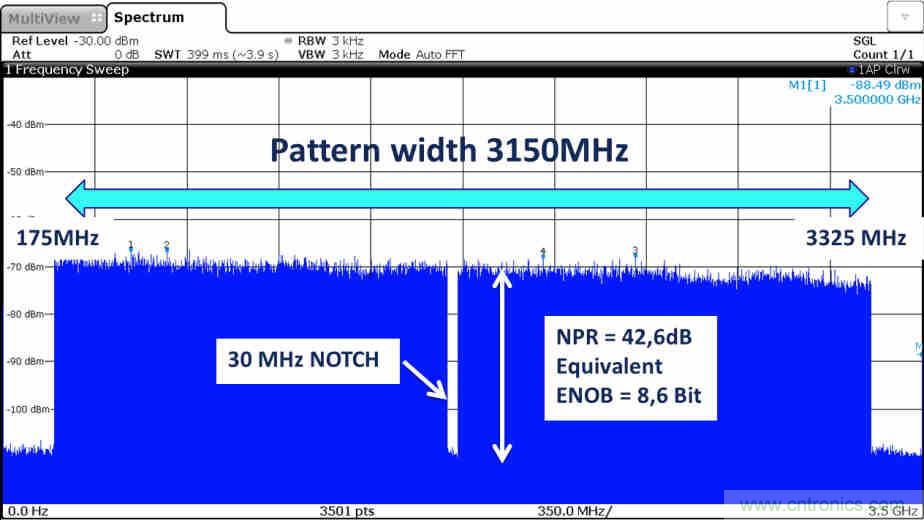

這款器件的寬帶NPR如下圖(圖9)所示。7Gsps的采樣率帶來3.150GHz的合成帶寬����。NPR是42.6dB,等效的有效位數(shù)(ENOB)為8.6����。注意NPR的平坦度一直到3325MHz的位置都相當好。

圖9: 3.15 GHz帶寬���,30MHz陷波的寬帶NPR

圖10中的第二個NPR特性在22GHz的范圍內(nèi)復(fù)制了3.150/2.700GHz的NPR譜���。這時DAC的采樣率為7/6Gsps����,工作模式是RF模式����。這些圖線表明提高采樣率帶來的優(yōu)勢之一����。它不僅影響DAC產(chǎn)生的最大瞬時帶寬,還擴展了高奈奎斯特區(qū)間的SINC特性和輸出功率���。

圖 10:多奈奎斯特區(qū)間的重復(fù)的NPR譜 —— 7Gsps時K波段的NPR有明顯提高

其他尖端的DAC

德州儀器最近有一款14bit 8.9Gsps RF DAC���,使用40nm CMOS工藝,支持4G LTE的應(yīng)用����。它的SFDR在8.9Gsps(Fout = 4300MHz)時是50dBc3。雖然這款DAC可以支持8.9Gsps的采樣率���,但是沒有任何超過4300MHz的測試數(shù)據(jù)���,而絕大多數(shù)的微波頻段都超過4300MHz����。

Analog Devices公司也在開發(fā)一款11/16bit, 12Gsps的DAC (AD9161/AD9162)���,其RF模式(也叫作混合模式)下的采樣率能達到12Gsps���。在RF模式下,因為每半個時鐘周期數(shù)據(jù)會反向���,似乎DAC在以12Gsps的采樣率采樣����。而對于RF模式下的EV12DS460A (圖5)���,數(shù)據(jù)反向被沒有被考慮進標稱的采樣率(6Gsps)���。因此,EV12DS460A和AD9161/62的采樣率是相同的����。這一點也可以由3GHz的瞬時帶寬證明���。

Analog Devices的器件在前兩個奈奎斯特區(qū)間的最佳的SFDR是65dBc (Fclock = 5Gsps, Fout = 4000MHz)。但是���,其性能在超過7500MHz的位置急劇下降����。輸出功率在Fout = 7500MHz時只有 -66dBm����,因此它無法在X波段和K波段很好地工作���。

結(jié)語

EV12DS460的發(fā)布給微波工程師帶來一款帶寬從DC一直到K波段頻率的寬帶DAC���。雖然這款器件并不是唯一的Gsps采樣率的DAC,但是如同上文所述���,它是第一款合成帶寬跨多個奈奎斯特區(qū)域����,同時保持優(yōu)秀的頻譜純度的DAC���。它為全新的毫米波應(yīng)用開拓了一個激動人心的新領(lǐng)域���。

參考文獻

From Infineon:

(1) J.Böck, H.Schäfer, K.Aufinger, R.Stengl, S.Boguth, R.Schreiter, M.Rest, H.Knapp, M.Wurzer, W.Perndl, T.Böttner, and T.F. Meister,

“SiGe bipolar technology for automotive radar applications” in Proc. Bipolar/BiCmos Circuits and Technology Meeting (BCTM),Montreal, Canada, Sep. 2004, pp.265-268

From Teledyne e2v:

(2) François Boré, Marc Wingender, Nicolas Chantier, Andrew Glascott-Jones, Emmanuel Dumaine, Carine Lambert, Sergio Calais « 3 GS/s 7GHz BW 12 Bit MuxDAC for Direct Microwave Signal Generation over L,S or C Bands” in Proc. COMCAS, Tel Aviv, Nov 2011

From TI:

(3) Ravinuthula, V., Bright, W., Weaver, M., Maclean, K., Kaylor, S., Balasubramanian, S., ...&Dwobeng, E. (2016, June). A 14-bit 8.9 GS/s RF DAC in 40nm CMOS achieving> 71dBc LTE ACPR at 2.9 GHz.In VLSI Circuits (VLSI-Circuits), 2016 IEEE Symposium on (pp. 1-2).IEEE.

推薦閱讀: