【導讀】信號完整性是指信號在傳輸路徑上的質(zhì)量,即信號在電路中能以正確的時序和電壓電平作出響應的能力。如果電路設計能夠達到把信號以規(guī)定的時序、持續(xù)時間和電壓幅值在互連系統(tǒng)中傳輸,就表明該電路具有良好的信號完整性。信號完整性問題體現(xiàn)在很多方面,當信號上升時間減小到一定的程度,電路板上的寄生電容和寄生電感開始導致一些可能影響電路性能的噪聲信號和瞬態(tài)信號時,就需要考慮信號的完整性問題,它可能會造成以下問題的發(fā)生。

1.延遲:延遲是指信號在PCB板的傳輸線上以有限的速度傳輸,信號從發(fā)送端發(fā)出到達接收端,其間存在一個傳輸延遲。信號延遲會對系統(tǒng)的時序產(chǎn)生影響;傳輸延遲主要取決于導線的長度和導線周圍介質(zhì)的介電常數(shù)。在高速數(shù)字系統(tǒng)中,信號傳輸線長度是影響時鐘脈沖相位差的最直接因素,時鐘脈沖相位差是指同時產(chǎn)生的兩個時鐘信號到達接收端的時間不同步。時鐘脈沖相位差降低了信號沿到達的可預測性,如果時鐘脈沖相位差太大,會在接收端產(chǎn)生錯誤的信號。

2. 反射:反射就是信號在信號線上的回波。當信號延遲時間遠大于信號跳變時間時,信號線必須當作傳輸線。當傳輸線的特性阻抗與負載阻抗不匹配時,信號功率(電壓或電流)的一部分傳輸?shù)骄€上并到達負載處,但是有一部分被反射了。若負載阻抗小于原阻抗,反射為負;反之,反射為正。布線的幾何形狀、不正確的線端接、經(jīng)過連接器的傳輸及電源平面不連續(xù)等因素的變化均會導致此類反射。

3.串擾:串擾是兩條信號線之間的耦合、信號線之間的互感和互容引起信號線上的噪聲。容性耦合引發(fā)耦合電流,而感性耦合引發(fā)耦合電壓。串擾噪聲源于信號線網(wǎng)之間、信號系統(tǒng)和電源分布系統(tǒng)之間、過孔之間的電磁耦合。串繞有可能引起假時鐘、間歇性數(shù)據(jù)錯誤等,對鄰近信號的傳輸質(zhì)量造成影響?,F(xiàn)實中,無法完全消除串擾,但可將其控制在系統(tǒng)所能承受的范圍之內(nèi)。PCB板層的參數(shù)、信號線間距、驅(qū)動端和接收端的電氣特性、基線端接方式對串擾都有一定的影響。

4.過沖和下沖:過沖就是第一個峰值或谷值超過設定電壓,對于上升沿,是指最高電壓;對于下降沿,是指最低電壓。下沖是指下一個谷值或峰值超過設定電壓。過分的過沖能夠引起保護二極管工作,導致其過早的失效。過分的下沖能夠引起假的時鐘或數(shù)據(jù)錯誤(誤操作)。

5.振蕩和環(huán)繞振蕩:振蕩現(xiàn)象是反復出現(xiàn)的過沖和下沖。信號的振蕩即是由線上過渡的電感和電容引起的振蕩,屬于欠阻尼狀態(tài),而環(huán)繞振蕩,屬于過阻尼狀態(tài)。振蕩和環(huán)繞振蕩同反射一樣也是由多種因素引起的,振蕩可以通過適當?shù)亩私佑枰詼p小,但是不可能完全消除。

為了提高高速信號質(zhì)量,需理解如下三個重要的電子學原理:

(1)電流是電子的流動;

(2)電流只能在閉合的回路中流動;

(3)電流在閉合回路中是恒定的。

一般來說,PCB設計者要花費大量的時間和精力對信號線的流動路徑進行設計規(guī)劃,并且處理返回信號,使信號可以尋找路徑返回。信號線完整性問題的一個基本原因就是對信號回流路徑的控制,在布置好元件的同時形成回路。

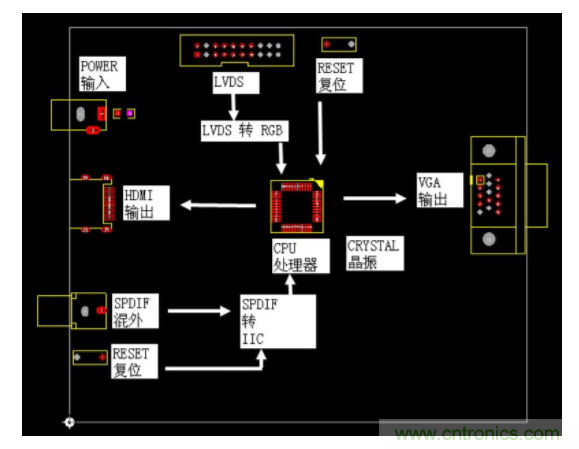

某網(wǎng)友模塊化飛線信號回路圖如下

推薦閱讀: