【導(dǎo)讀】在高速PCB電路設(shè)計(jì)過程中,經(jīng)常會(huì)遇到信號(hào)完整性問題,導(dǎo)致信號(hào)傳輸質(zhì)量不佳甚至出錯(cuò)。那么如何區(qū)分高速信號(hào)和普通信號(hào)呢?很多人覺得信號(hào)頻率高的就是高速信號(hào),實(shí)則不然。任何信號(hào)都可以由正弦信號(hào)的N次諧波來表示,而信號(hào)的最高頻率或者信號(hào)帶寬才是衡量信號(hào)是否是高速信號(hào)的標(biāo)準(zhǔn)。

1、隔離

一塊PCB板上的元器件有各種各樣的邊值(edge rates)和各種噪聲差異。對(duì)改善SI最直接的方式就是依據(jù)器件的邊值和靈敏度,通過PCB板上元器件的物理隔離來實(shí)現(xiàn)。

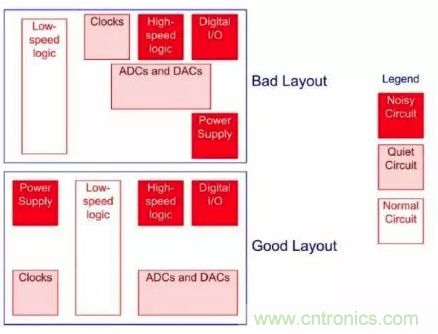

圖1是一個(gè)實(shí)例。在例子中,供電電源、數(shù)字I/O端口和高速邏輯這些對(duì)時(shí)鐘和數(shù)據(jù)轉(zhuǎn)換電路的高危險(xiǎn)電路將被特別考慮。

第一個(gè)布局中放置時(shí)鐘和數(shù)據(jù)轉(zhuǎn)換器在相鄰于噪聲器件的附近。噪聲將會(huì)耦合到敏感電路及降低他們的性能。第二個(gè)布局做了有效的電路隔離將有利于系統(tǒng)設(shè)計(jì)的信號(hào)完整性。

2、阻抗、反射及終端匹配

阻抗控制和終端匹配是高速電路設(shè)計(jì)中的基本問題。通常每個(gè)電路設(shè)計(jì)中射頻電路均被認(rèn)為是最重要的部分,然而一些比射頻更高頻率的數(shù)字電路設(shè)計(jì)反而忽視了阻抗和終端匹配。

由于阻抗失配產(chǎn)生的幾種對(duì)數(shù)字電路致命的影響,參見下圖:

a.數(shù)字信號(hào)將會(huì)在接收設(shè)備輸入端和發(fā)射設(shè)備的輸出端間造成反射。反射信號(hào)被彈回并且沿著線的兩端傳播直到最后被完全吸收。

b.反射信號(hào)造成信號(hào)在通過傳輸線的響鈴效應(yīng),響鈴將影響電壓和信號(hào)時(shí)延和信號(hào)的完全惡化。

c.失配信號(hào)路徑可能導(dǎo)致信號(hào)對(duì)環(huán)境的輻射。

由阻抗不匹配引起的問題可以通過終端電阻降到最小。終端電阻通常是在靠近接收端的信號(hào)線上放置一到兩個(gè)分立器件,簡(jiǎn)單的做法就是串接小的電阻。

終端電阻限制了信號(hào)上升時(shí)間及吸收了部分反射的能量。值得注意的是利用阻抗匹配并不能完全消除破壞性因素。然而認(rèn)真的選用合適的器件,終端阻抗可以很有效的控制信號(hào)的完整性。

并不是所有的信號(hào)線都需要阻抗控制,在一些諸如緊湊型 PCI 規(guī)格要求中的特征阻抗和終端阻抗特性。對(duì)于別的沒有阻抗控制規(guī)范要求的其他標(biāo)準(zhǔn)以及設(shè)計(jì)者并沒有特意關(guān)注的。

最終的標(biāo)準(zhǔn)可能發(fā)生變化從一個(gè)應(yīng)用到另一個(gè)應(yīng)用中。因此需要考慮信號(hào)線的長(zhǎng)度(相關(guān)與延遲 Td)以及信號(hào)上升時(shí)間(Tr)。通用的對(duì)阻抗控制規(guī)則是 Td(延遲)應(yīng)大于 Tr 的 1/6。

3、內(nèi)電層及內(nèi)電層分割

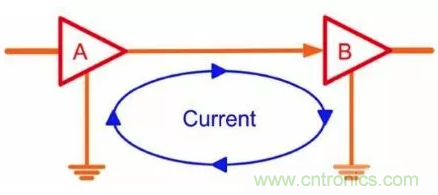

在電流環(huán)路設(shè)計(jì)中會(huì)被數(shù)字電路設(shè)計(jì)者忽視的因素,包括對(duì)單端信號(hào)在兩個(gè)門電路間傳送的考慮(圖2)。從門 A 流向門 B 的電流環(huán)路,然后再從地平面返回到門 A。

圖2 門電路電流環(huán)路

門電路電流環(huán)路中存在兩個(gè)潛在的問題:

a、 A 和 B 兩點(diǎn)間地平面需要被連接通過一個(gè)低阻抗的通路

如果地平面間連接了較大的阻抗,在地平面引腳間將會(huì)出現(xiàn)電壓倒灌。這就必將會(huì)導(dǎo)致所有器件的信號(hào)幅值的失真并且疊加輸入噪聲。

b、 電流回流環(huán)的面積應(yīng)盡可能的小

環(huán)路好比天線。通常說話,一種更大環(huán)路面積將會(huì)增大了環(huán)路輻射和傳導(dǎo)的機(jī)會(huì)。每一個(gè)電路設(shè)計(jì)者都希望回流電流都可直接沿著信號(hào)線,這樣就最小的環(huán)路面積。

用大面積接地可以同時(shí)解決以上兩個(gè)問題。大面積接地可以提供所有接地點(diǎn)間小的阻抗,同時(shí)允許返回電流盡量直接沿著信號(hào)線返回。

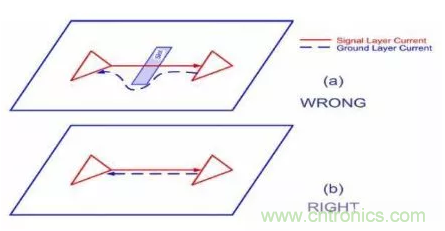

在 PCB 設(shè)計(jì)中一個(gè)常見的錯(cuò)誤是在層間打過孔和開槽。圖3顯示了當(dāng)一條信號(hào)線在一個(gè)開過槽的不同層上的電流流向?;芈冯娏鲗⒈黄壤@過開槽,這就必然會(huì)產(chǎn)生一個(gè)大的環(huán)流回路。

圖3 PCB層間回路電流流向

通常而言,在地電源平面上是不可以開槽的。然而,在一些不可避免要開槽的場(chǎng)合,PCB 設(shè)計(jì)者必須首先確定在開槽的區(qū)域沒有信號(hào)回路經(jīng)過。

同樣的規(guī)則也適用于混合信號(hào)電路 PCB 板中除非用到多個(gè)地層。特別是在高性能ADC電路中可以利用分離模擬信號(hào)、數(shù)字信號(hào)及時(shí)鐘電路的地層有效的減少信號(hào)間的干擾。

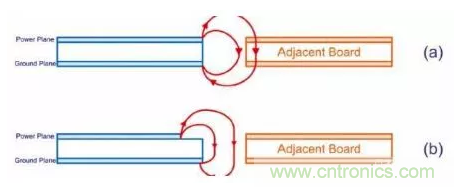

需要再次強(qiáng)調(diào)的,在一些不可避免要開槽的場(chǎng)合,PCB 設(shè)計(jì)者必須首先確定在開槽的區(qū)域沒有信號(hào)回路經(jīng)過。在帶有一個(gè)鏡像差異的電源層中也應(yīng)注意層間區(qū)域的面積(圖4)。

在板卡的邊緣存在電源平面層對(duì)地平面層的輻射效應(yīng)。從邊沿泄漏的電磁能量將破壞臨近的板卡。見下圖4a。適當(dāng)?shù)臏p少電源平面層的面積(圖4 b),以至于地平面層在一定的區(qū)域內(nèi)交疊。這將減少電磁泄漏對(duì)鄰近板卡的影響。

圖4 地電層的輻射效應(yīng)

4、串?dāng)_

在PCB設(shè)計(jì)中,串?dāng)_問題是另一個(gè)值得關(guān)注的問題。下圖中顯示出在一個(gè)PCB中相鄰的三對(duì)并排信號(hào)線間的串?dāng)_區(qū)域及關(guān)聯(lián)的電磁區(qū)。當(dāng)信號(hào)線間的間隔太小時(shí),信號(hào)線間的電磁區(qū)將相互影響,從而導(dǎo)致信號(hào)的變化就是串?dāng)_。

串?dāng)_可以通過增加信號(hào)線間距解決。然而,PCB 設(shè)計(jì)者通常受制于日益緊縮的布線空間和狹窄的信號(hào)線間距;由于在設(shè)計(jì)中沒有更多的選擇,從而不可避免的在設(shè)計(jì)中引入一些串?dāng)_問題。顯然,PCB 設(shè)計(jì)者需要一定的管理串?dāng)_問題的能力。

通常業(yè)界認(rèn)可的規(guī)則是 3W 規(guī)則,即相鄰信號(hào)線間距至少應(yīng)為信號(hào)線寬度的 3 倍。但是,實(shí)際工程應(yīng)用中可接受的信號(hào)線間距依賴于實(shí)際的應(yīng)用、工作環(huán)境及設(shè)計(jì)冗余等因素。

信號(hào)線間距從一種情況轉(zhuǎn)變成另一種以及每次的計(jì)算。因此,當(dāng)串?dāng)_問題不可避免時(shí),就應(yīng)該對(duì)串?dāng)_定量化。這都可以通過計(jì)算機(jī)仿真技術(shù)表示。利用仿真器, 設(shè)計(jì)者可以決定信號(hào)完整性效果和評(píng)估系統(tǒng)的串?dāng)_影響效果。

5、電源去耦

電源去耦是數(shù)字電路設(shè)計(jì)中慣例,退耦有助于減少電源線上噪聲問題。迭加在電源上的高頻噪聲將會(huì)對(duì)相鄰的數(shù)字設(shè)備都會(huì)帶來問題。典型的噪聲于地彈、信號(hào)輻射或者數(shù)字器件自身。

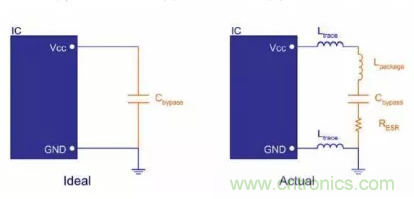

最簡(jiǎn)單的解決電源噪聲方式是利用電容對(duì)地上的高頻噪聲去耦。理想的退耦電容為高頻噪聲提供了一條對(duì)地的低阻通路,從而清除了電源噪聲。

依據(jù)實(shí)際應(yīng)用選擇去耦電容,大多數(shù)的設(shè)計(jì)者會(huì)選擇表貼電容在盡可能靠近電源引腳,而容值應(yīng)大到足夠?yàn)榭深A(yù)見的電源噪聲提供一條低阻對(duì)地通路。

采用退耦電容通常會(huì)遇到的問題是不能將退耦電容簡(jiǎn)單的當(dāng)成電容。有以下幾種情況:

a、 電容的封裝會(huì)導(dǎo)致寄生電感;

b、 電容會(huì)帶來一些等效電阻;

c、 在電源引腳和退耦電容間的導(dǎo)線會(huì)帶來一些等效電感;

d、 在地引腳和地平面間的導(dǎo)線會(huì)帶來一些等效電感;

由此而引發(fā)的效應(yīng):

a、 電容將會(huì)對(duì)特定的頻率引發(fā)共振效應(yīng)和由其產(chǎn)生的網(wǎng)絡(luò)阻抗對(duì)相鄰頻段的信號(hào)造成更大的影響;

b、 等效電阻(ESR)還將影響對(duì)高速噪聲退耦所形成的低阻通路;

圖5 現(xiàn)實(shí)中的去耦

以下總結(jié)了由此對(duì)一個(gè)數(shù)字設(shè)計(jì)者產(chǎn)生的效應(yīng):

a、 從器件上 Vcc 和 GND 引腳引出的引線需要被當(dāng)作小的電感。因此建議在設(shè)計(jì)中盡可能使 Vcc 和 GND 的引線短而粗。

b、 選擇低 ESR 效應(yīng)的電容,這有助于提高對(duì)電源的退耦;

c、 選擇小封裝電容器件將會(huì)減少封裝電感。改換更小封裝的器件將導(dǎo)致溫度特性的變化。

因此在選擇一個(gè)小封裝電容后,需要調(diào)整設(shè)計(jì)中器件的布局。在設(shè)計(jì)中,用 Y5V 型號(hào)的電容替換 X7R 型號(hào)的電容器件,可保證更小的封裝和更低的等效電感,但同時(shí)也會(huì)為保證高的溫度特性花費(fèi)更多的器件成本。

在設(shè)計(jì)中還應(yīng)考慮用大容量電容對(duì)低頻噪聲的退耦。采用分離的電解電容和鉭電容可以很好的提高器件的性價(jià)比。