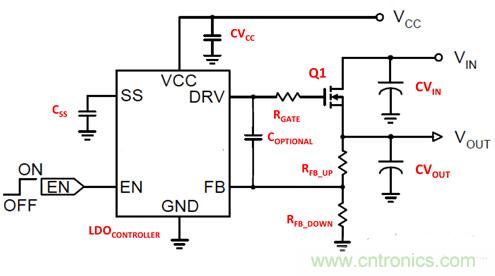

【導讀】在亞洲生活和工作讓我遇到了很多有趣的支持問題。例如,最近有人問我TI有沒有針對低壓降控制器的跨設備。該控制器位于小外形晶體管(SOT)-236封裝內,該封裝在印刷電路板(PCB)上所占面積為3mm×3mm。圖1所示為所推薦的控制器原理圖。

圖1:簡單的低壓降控制器

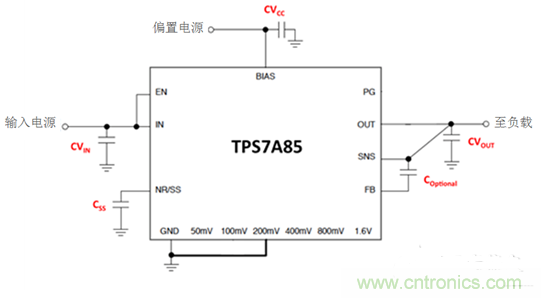

從表面來看,使用高電流穩(wěn)壓器似乎是不錯的選擇。了解到設計工程師想要支持1.35VIN 到1.0VOUT的最大4A電流后,我推薦其使用TPS7A85。TPS7A85并非控制器,但其可以完全集成到3.5mm×3.5mm、20引腳、方形扁平無引腳(QFN)封裝的4A LDO電壓穩(wěn)壓器中。很顯然,這一封裝比SOT-236要略微大一些。

我當即得到的回復是,“TPS7A85太復雜了。”有時,引腳越多意味著越復雜;然而,在TPS7A85中,更多的引腳實際上卻轉換為更少的組件。查看一下圖2中的TPS7A85等效原理圖,你可以發(fā)現外部組件數量從9個減少到了5個。

輸入電源

偏置電源

至負載

圖2:TPS7A85用作4A的低壓降穩(wěn)壓器

為什么少了四個組件呢?TPS7A85具有TI的可調輸出功能,用戶可以利用電壓設置引腳動態(tài)地設置VOUT。只要這些引腳中的其中一個接地,相應的電壓便會加上800mV內部參考電壓。因此,通過將200mV引腳接地,VOUT便立即變?yōu)?.0V。

利用這一功能,您可以通過簡單地將合適的電壓設置引腳接地,在800mV到3.95V間調節(jié)電壓,從而打造出想要的輸出電壓。該方法可量化的好處有:

確保1%精度的輸出調節(jié)。

無需購買精密反饋電阻器來設置VOUT(當然,如果您希望的話,仍可以搭配使用FB引腳和外部電阻器)。

可以在應用中動態(tài)設置VOUT。

搭配使用低壓降控制器后,總效率僅為1/1.35V,或74%。功率FET中的總功耗最差為4A ×4350mV,或1.4W。結果表明,這與您通過低壓降穩(wěn)壓器得到的效率一樣。

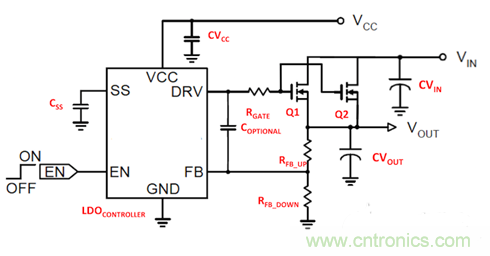

為了管理熱量,控制器使用兩個外部FET幫助散熱,如圖3所示。

圖3:低壓降控制器驅動雙通道FET

若您希望使用控制器,建議您加裝一個RGATE,以幫助確保柵極驅動布局盡可能對稱,以便Q1和Q2能夠恰當地分享電流。在本應用中,FET位于5mm×6mm大小的封裝中,其所占空間比控制器本身還要大六倍多。

TPS7A85封裝尺寸僅為3.5mm × 3.5mm,因此其熱性能可能沒有低壓降控制器好。讓我們來比較一下。搭配控制器,FET的結至環(huán)境熱阻(TJA)溫度為25°C/W。因此,在峰值電流時功耗為1.4W,升溫應約為1.4W × 25°C/W,或35°C。升溫為17.5°C/FET——假設兩個FET的升溫幅度相同。這似乎很棒。與TPS7A85相比較,效果如何呢?

TPS7A85 的TJA為35.4°C/W,因此峰值功率時升溫為1.4W × 35.4°C/W,或49.6°C。表面上看,似乎表現不如控制器,但真是這樣嗎?讓我們來看下集成低壓降穩(wěn)壓器相較于低壓降控制器的切實優(yōu)勢:

熱關機——低壓降控制器沒有檢測FET溫度的能力。而TPS7A85有。

電流限制——低壓降控制器唯一的職責就是調節(jié)VOUT。當負載電流過高時,它沒有限制電流或關機的功能。而 TPS7A85 有。

穩(wěn)定性——若您想確保在應用中低壓降控制器與FET、寄生電容和電感穩(wěn)定地協作,就必須加裝額外的組件來測量環(huán)路穩(wěn)定性。而使用TPS7A85,則無需這么麻煩。

尺寸——低壓降控制器帶有外部FET,因此所占空間更大。而TPS7A85則不同。

精度——本應用中,低壓降控制器的總體精度為2.5%。外部電阻器最壞情況下則為4.5%。而TPS7A85總精度則高于1%。

噪音——低壓降控制器在數據表上并未提及這一點。TPS7A85在1VOUT條件下的噪音為~5μVRMS10-100KHz。

該清單中的最后兩條優(yōu)勢尤其值得注意,因為大多數應用都放棄直流/直流轉換器,而選擇低壓降控制器或低壓降穩(wěn)壓器為FPGA或DSP的精密VCORE軌道或精密ADC/DAC供電。

綜上所述,低壓降穩(wěn)壓器可以說是解決這一問題最簡單的方法。在您的下一個設計中,可以考慮使用TI的TPS7A85高電流、高精度、低噪音低壓降穩(wěn)壓器。