【導(dǎo)讀】不久前�,Dialog半導(dǎo)體公司與格芯(GLOBALFOUNDRIES)簽訂了協(xié)議�,向其授權(quán)導(dǎo)電橋式隨機(jī)存取存儲器(Conductive Bridging RAM�;CBRAM)技術(shù)�����。CBRAM屬于通用的存儲器技術(shù),應(yīng)用范圍非常廣�����,從可穿戴設(shè)備到智能手機(jī)等�����。其性能優(yōu)勢主要體現(xiàn)在低功耗��。

CBRAM技術(shù)由Dialog于2020年收購的Adesto Technologies首創(chuàng)并獲得專利�。有了這項(xiàng)專利許可,格芯將在其22FDX平臺上提供這種配置��,并在未來幾年將其擴(kuò)展到其他平臺��。

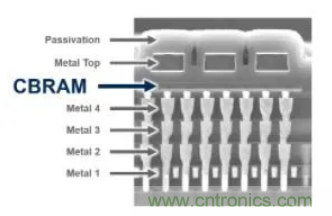

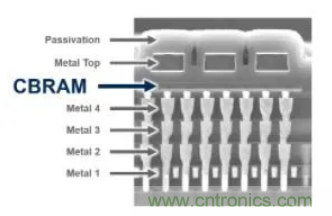

存儲器行業(yè)正在經(jīng)歷工業(yè)和技術(shù)層面的深刻發(fā)展。新的技術(shù)知識催生了NVM(非易失性存儲器)元件在電阻上做了改變�����,并擴(kuò)展了功能�,以適用于光學(xué)和電氣設(shè)備。CBRAM存儲器是通過采用專利金屬化技術(shù)��,在標(biāo)準(zhǔn)CMOS互連金屬層之間采用電介質(zhì)疊層而創(chuàng)建的��。CBRAM工藝改變了其存儲單元的電阻�,提供了更高的可靠性。

CBRAM技術(shù)

Dialog的CBRAM技術(shù)適用于像所有物聯(lián)網(wǎng)解決方案一樣要求低功耗的應(yīng)用�����。應(yīng)用范圍包括從5G到人工智能�����,這些領(lǐng)域?qū)ψx/寫速度有很高要求��,但同時要求降低生產(chǎn)成本��。像工業(yè)應(yīng)用這種需要對嚴(yán)苛環(huán)境有一定耐受能力的應(yīng)用也偏愛使用該技術(shù)�,該技術(shù)也可用于汽車行業(yè)。

近期��,Dialog半導(dǎo)體公司工業(yè)應(yīng)用IC副總裁Raphael Mehrbians在接受EE Times Europe采訪時�����,分析了CBRAM的重要性��,談到了Dialog在收購Adesto之后采取的戰(zhàn)略��。與格芯的合作證明了該技術(shù)得以很好地使用��。

與傳統(tǒng)的嵌入式NVM不同�,CBRAM技術(shù)不需要高電壓來改變記憶單元狀態(tài)。“這不僅使它能夠集成到標(biāo)準(zhǔn)邏輯中�,還意味著進(jìn)出陣列的數(shù)據(jù)路徑的電壓相對較低。為了從存儲器中讀取數(shù)據(jù)��,將低電壓施加到選中的柵極�,使用典型的傳感技術(shù)即可提取記憶單元的電阻。” Mehrbians說�����。

CBRAM產(chǎn)品的截面展示了其易于在標(biāo)準(zhǔn)CMOS工藝中集成(圖片來源:Dialog半導(dǎo)體公司)

● 該技術(shù)的主要電氣特性可以總結(jié)如下:

● CBRAM單元由1個選擇的晶體管和1個可編程非易失性電阻組成�����。

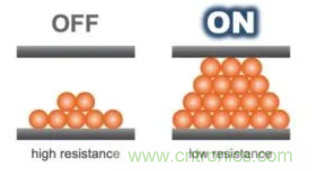

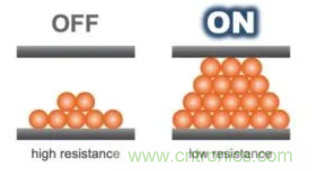

● CBRAM是一種電化學(xué)單元,它通過原子的電動運(yùn)動來改變狀態(tài)�����。

● 邏輯1由具有導(dǎo)通時的低電阻單元表示�。

● 邏輯0由具有截止時的高電阻單元表示。

● 通過施加相反極性的電壓脈沖將其編程為1和將其擦除為0�。

● 高可靠性、100K 擦寫次數(shù)��、10年數(shù)據(jù)存儲�。

● 高熱穩(wěn)定性,兼容回流焊

● 寫 @ <3V

● 讀 @ <0.8V

正如Dialog所指出的��,該技術(shù)的主要優(yōu)勢是功耗和成本��。“CBRAM技術(shù)的固有特點(diǎn)是低電壓和低功耗�。對于需要低電壓/低功耗NVM的嵌入式系統(tǒng)而言,這是很重要的優(yōu)勢�����。CBRAM簡單的單元結(jié)構(gòu)僅通過增加幾道后道工序的掩膜即可方便地插入標(biāo)準(zhǔn)CMOS邏輯中�����,顯著低于傳統(tǒng)嵌入式閃存所需的數(shù)量。與其他NVM技術(shù)相比�,后道工序的插入還提供了優(yōu)越的可擴(kuò)展性�。”Mehrbians說。

CBRAM將于2022年在格芯的22FDX平臺上作為嵌入式NVM選項(xiàng)提供投入生產(chǎn)�����。當(dāng)電源斷開時�����,像RAM(隨機(jī)訪問存儲器)這樣的易失性存儲器會丟失它們存儲的數(shù)據(jù)�,而NVM會在電源斷開后保存存儲在其中的數(shù)據(jù)。

“傳統(tǒng)嵌入式NVM的挑戰(zhàn)包括:擴(kuò)展到28nm以下的先進(jìn)工藝節(jié)點(diǎn)�����、傳統(tǒng)CMOS的成本顯著增加��、 以及在訪問時間和功耗方面的性能��。”Mehrbians說��。

圖2:CBRAM的工作原理(圖片來源:Dialog半導(dǎo)體公司)

他補(bǔ)充說:“該技術(shù)適用的應(yīng)用包括先進(jìn)MCU、連接性產(chǎn)品和安全性應(yīng)用�����。這些通常是更智能的終端設(shè)備所要求的��,這些設(shè)備需要更多的智能(AI)�����,以及安全性和先進(jìn)通信協(xié)議��,如NB-IoT��。”

Dialog強(qiáng)調(diào)了嵌入式NVM與外部存儲器相比的優(yōu)勢�����,主要是因?yàn)镮O沒有外露�。在CBRAM中,實(shí)際上不可能通過物理分析來檢測記憶單元的狀態(tài)��。此外�,記憶單元的狀態(tài)不受磁場和輻射的影響(圖1和2)。

通過IP定制,客戶可以修改CBRAM單元來優(yōu)化他們的SoC設(shè)計(jì)��,提高安全性�,或者可以對單元進(jìn)行調(diào)整以用于新的應(yīng)用。

作者:Maurizio Di Paolo Emilio��,EE Times Europe

免責(zé)聲明:本文為轉(zhuǎn)載文章�����,轉(zhuǎn)載此文目的在于傳遞更多信息��,版權(quán)歸原作者所有�����。本文所用視頻�、圖片��、文字如涉及作品版權(quán)問題��,請聯(lián)系小編進(jìn)行處理�����。

推薦閱讀: